Il test mediante JTAG boundary scan, una metodologia di collaudo che consente di rilevare rapidamente difetti di produzione, minimizzando gli accessi fisici su schede ad elevata complessità

Il test di fine linea di prodotti elettronici è da sempre un processo cruciale che non solo dà evidenza del funzionamento e della qualità del prodotto, ma anche della bontà della sua progettazione e del processo di produzione. Se materialmente il collaudo si pone come ultimo step prima della distribuzione, occorre tenere presente come si farà il test del prodotto fin dalle prime fasi di design, in modo che sia efficace, affidabile, ripetibile, con tempi congrui a produzioni che hanno un time to market sempre più breve.

I sistemi di collaudo tradizionali prevedono la contattazione fisica del DUT (Device under test) mediante aghi o sonde mobili. L’evoluzione dell’elettronica, tuttavia, ci mostra schede con integrati sempre più piccoli, con elevato numero di pin, difficili o impossibili da raggiungere (BGA), con connessioni multistrato non accessibili, ponendo restrizioni funzionali importanti a piattaforme di test e con costi non ricorrenti molto elevati. Negli ultimi anni il fenomeno dello shortage ha evidenziato anche un’altra problematica che trasversalmente influenza tutte le fasi produttive: molto spesso il design di prodotto deve essere modificato per mancanza di determinati componenti. Anche i sistemi di test, quindi, devono poter essere facilmente adattati e riconfigurati in tempi brevi.

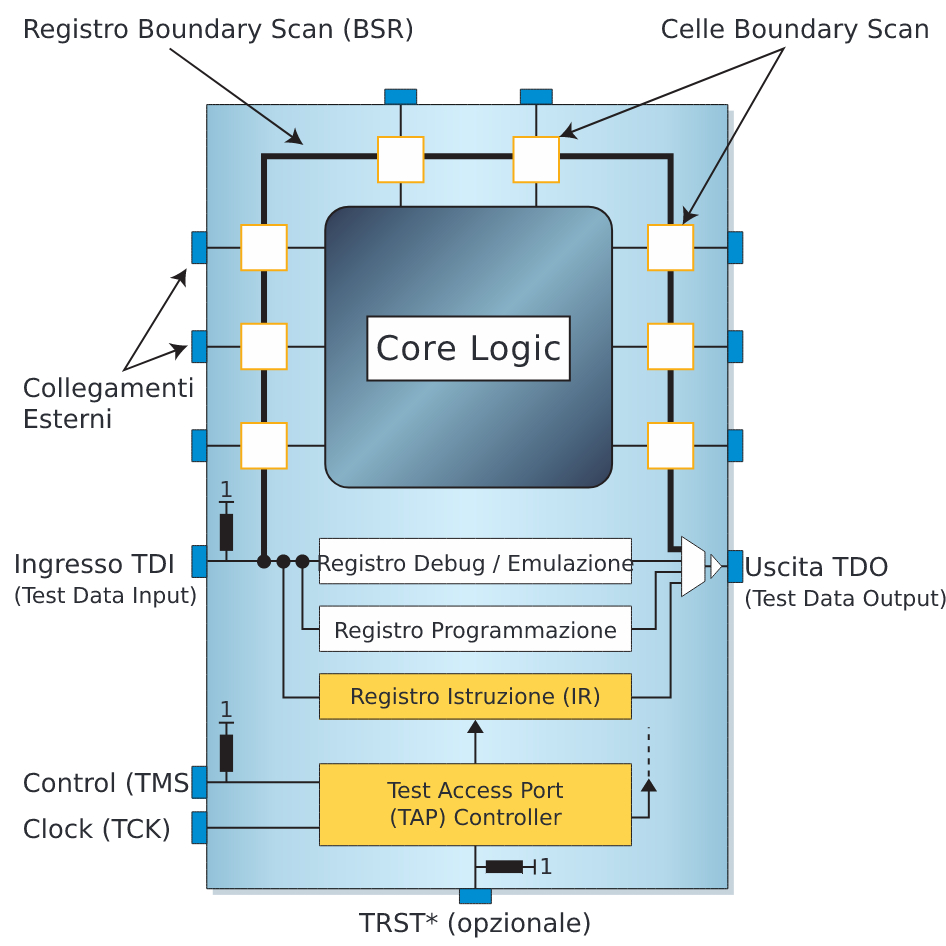

Fig. 1 – Architettura JTAG/Boundary scan all’interno di un componente compliant

Fig. 1 – Architettura JTAG/Boundary scan all’interno di un componente compliant

Il test JTAG boundary scan

Per ovviare a queste problematiche per tutte le schede elettroniche con componenti digitali di media/elevata complessità è possibile usare la metodologia di test JTAG boundary scan.

Seguendo lo standard JTAG IEEE 1149.x, il boundary scan - implementato direttamente nel core logic dal chip vendor - prevede una circuiteria all’interno del componente in grado di rendere disponibili dei test point virtuali che simulano gli ingressi e le uscite presenti sul componente e descritti in un file denominato BSDL (Boundary Scan Description Language).

Molto spesso questa interfaccia viene utilizzata per accedere alle funzioni di debug/emulazione del componente o per la programmazione di FPGA/CPLD. Tuttavia il boundary scan nasce proprio come protocollo di collaudo, come dice il nome JTAG che sta per Joint Test Action Group, mettendo a disposizione un potentissimo strumento di collaudo per la produzione, per l’analisi guasti e per il debug di schede elettroniche.

Come funziona il boundary scan?

Mediante l’interfacciamento fisico a quattro segnali detti Test Access Port (TAP) si può interagire con un registro specificatamente implementato nel componente per il test, il Boundary Scan Register (BSR). Come il suo nome suggerisce, i singoli bit (o celle) sono implementati in prossimità della periferia (boundary) del componente tra il core e i pin esterni con cui è collegato alla scheda: il test JTAG è definito per questo anche Boundary Scan.

Le celle boundary scan possono operare in due modalità diverse. Nella modalità “funzionale” la scheda lavora normalmente e le celle non hanno alcun effetto sul funzionamento del componente. Nella modalità “test” le celle isolano il core dai suoi pin esterni e possono essere utilizzate per controllare dei valori forzati su una net da un componente JTAG o per monitorarne lo stato. La possibilità di isolare il controllo dei pin dalla funzionalità del componente rende il test boundary scan decisamente più semplice di un tradizionale test funzionale, in quanto non è richiesta nessuna configurazione per poter abilitare i pin; questo permette di verificare la scheda senza necessità di un firmware di test. Potendo monitorare tramite un TAP a 4 pin tutti i segnali abilitati su una scheda, il JTAG riduce significativamente l’accesso fisico richiesto per il test.

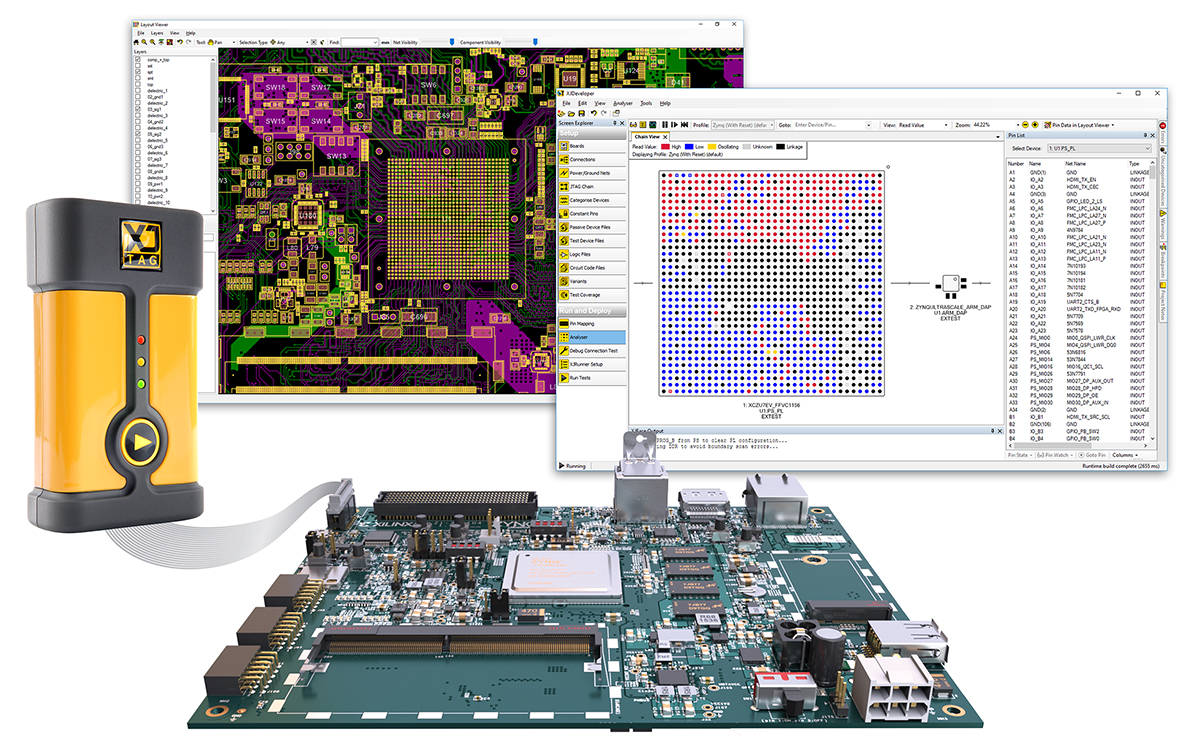

Fig. 2 – Test Boundary Scan: controllo dei pin e visualizzazione guasto su layout viewer

Fig. 2 – Test Boundary Scan: controllo dei pin e visualizzazione guasto su layout viewer

Ci sono due diversi modi in cui è possibile utilizzare le proprietà del boundary scan in collaudo. Il primo, il test di connessione, fornisce una buona copertura per il rilevamento di eventuali cortocircuiti. Esso si basa puramente sulle proprietà dei componenti JTAG, sulle connessioni della scheda e – nel caso di XJTAG – sul funzionamento dei componenti logici presenti nel circuito. Il secondo amplia la copertura di test utilizzando i componenti abilitati al JTAG per comunicare con altri componenti non-JTAG, come RAM DDR e flash.

Il test di connessione JTAG verifica quindi che su una scheda elettronica le connessioni attorno ai dispositivi abilitati al JTAG rispettino quelle specificate nel progetto: se due pin con accesso JTAG devono essere connessi, il test assicurerà che un pin possa essere controllato dall’altro, se non devono essere connessi, vengono testati per individuare eventuali guasti di cortocircuito pilotando un pin e verificando che i valori forzati non siano letti sugli altri pin.

Resistenze di pull-up/pull-down mancanti, corti verso massa e alimentazioni possono essere individuati dal test di connessione, come anche eventuali problemi che riguardano componenti logici il cui comportamento può essere descritto in una tabella della verità.

Il test di componenti non JTAG

Mentre i dispositivi principali, come processori e FPGA, sono normalmente abilitati al JTAG, su ogni scheda elettronica ci saranno molti altri componenti che non lo sono. DDR, SDRAM, SRAM, flash, Ethernet PHY, sensori di temperatura SPI e I2C, clock real time, ADC e DAC sono solo alcuni esempi.

Il test di connessione fornirà un’ottima copertura per i guasti di cortocircuito sulle net che collegano questi componenti a quelli JTAG. Tuttavia, questo test non è in grado di verificare eventuali guasti di circuito aperto sia sul componente JTAG che su quello non JTAG. Per aggiungere questa copertura è possibile interagire con il componente non-JTAG sfruttando le funzionalità boundary scan fornite dal componente JTAG. Quindi, se la comunicazione tra i due componenti può essere verificata, si possono scartare guasti dati da circuiti aperti: sarà possibile, per esempio, accendere un LED sulla scheda verificandone il funzionamento o scrivere dati nell’array di memoria di una RAM e poi farne la lettura.

Fig. 3 – Integrazione test boundary in una fixture per test funzionale con controller JTAG per esecuzione del test in parallelo su quattro DUT

I vantaggi della metodologia

Il test boundary scan non è solo estremamente veloce (un connection test impiega tipicamente pochi secondi), ma dà informazioni precise in merito ai guasti rilevati, facilitando una rapida riparazione. I tool software più avanzati forniscono anche la possibilità di visualizzare la posizione fisica di un guasto sul layout e l’area in cui il guasto è localizzato sullo schema elettrico, integrando potenti strumenti quali Schematic Viewer e Layout Viewer, permettendo di ispezionare i singoli layer anche uno alla volta.

Poiché l’hardware di interfacciamento è costituito solo da un controller JTAG e il test boundary scan può essere eseguito senza necessità di sviluppo di firmware e apparecchiature specializzate, esso è una metodologia efficacissima già durante le fasi di board bring-up per individuare eventuali difetti di fabbricazione molto prima della messa in produzione.

Anche i tempi di sviluppo del software di collaudo sono estremamente ridotti poiché il JTAG fornisce un’interfaccia standard semplificata per controllare i pin di I/O utilizzati per interagire con le varie periferiche, che è la stessa per tutti i dispositivi abilitati al JTAG, garantendo che dei modelli generici possano essere utilizzati durante la realizzazione degli apparati di test. Questo ovviamente porta anche ad altri due vantaggi: nel caso di sostituzione di un componente gli interventi per adattare il software e l’hardware saranno minimi e lo stesso tool potrà essere sfruttato anche per prodotti nuovi, ammortizzando i costi della tecnologia trasversalmente.

Quando il boundary scan non è sufficiente

Nessuna tipologia di test da sola è efficace al 100%, ogni approccio avrà limiti e vantaggi, i migliori risultati in termini di copertura si ottengono mettendo insieme più metodologie. Anche in questo caso il test boundary scan è un ottimo alleato perché si presta a una facile integrazione con sistemi sia ICT, sia funzionali. Dal punto di vista hardware, poiché la porta JTAG è tipicamente già contattata, l’integrazione del controller è semplice e immediata e non richiede tempi e lavorazioni meccaniche invasive, anche nel caso di sistemi già sviluppati. Dal punto di vista software, alcune piattaforme sono già ottimizzate per l’integrazione in diversi ambienti di sviluppo tipicamente impiegati nel testing quali .NET, LabVIEW, TestStand. Una piattaforma combinata con il boundary scan permetterà di coprire quelle aree digitali di difficile o impossibile accesso, semplificando anche lo sviluppo delle attrezzature.

L’utilizzo di piattaforme di sviluppo user-friendly permettono di impratichirsi e rendersi autonomi nello sviluppo in tempi rapidi, avendo al proprio fianco uno strumento potente e capace di supportare tutte le fasi di sviluppo, prototipazione, produzione e repair del prodotto.