Le tecnologie avanzate di packaging dei semiconduttori sono fondamentali a causa del rallentamento della legge di Moore e dell'aumento dei costi di sviluppo e produzione dei circuiti integrati monolitici Si. Inizialmente, i componenti venivano confezionati e integrati singolarmente a livello di scheda pcb, ma man mano che i dispositivi diventano più piccoli e richiedono maggiori capacità di elaborazione, l'integrazione dei componenti deve essere spinta oltre il livello di scheda. L'integrazione a livello di package è stato il primo passo avanti, seguito dall'integrazione a livello di wafer, che offre una densità di connessione almeno dieci volte superiore, un ingombro ridotto adatto ad applicazioni sensibili alle dimensioni e prestazioni superiori.

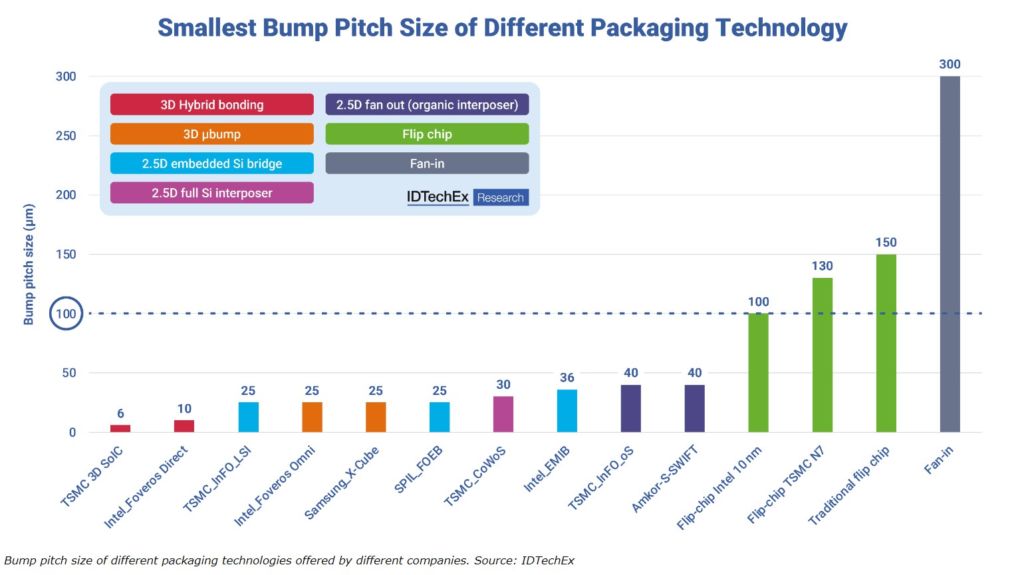

L'integrazione a livello di wafer comprende le tecnologie di packaging fan-in, core fan-out, fan-out ad alta densità, IC 2,5D e IC 3D. Tuttavia, solo quelle con un passo di bumping inferiore a 100 µm sono considerate tecnologie di packaging per semiconduttori "avanzate". Tra queste rientrano le tecnologie di confezionamento ad alta densità con fan-out, IC 2,5D e IC 3D.

Il passaggio da un'integrazione ibrida 2,5D a un'integrazione verticale 3D completa è fondamentale per le future applicazioni incentrate sui dati e in questo articolo ci concentreremo su questa transizione.

La sfida principale nel passaggio da 2,5D a 3D consiste nel ridimensionare le dimensioni del bumping pitch. In un pacchetto IC 2.5D, le dimensioni del bump pitch variano tra 25 e 40 µm, a seconda del materiale dell'interposer. Tuttavia, per un pacchetto di impilamento 3D, le dimensioni del bump devono essere ridotte a una sola cifra di µm o addirittura a una dimensione inferiore a 1 µm. TSMC ha comunicato che il bump pitch per lo stacking di chip N7/N6 è di 9 µm e di 6 µm per lo stacking di chip N5. Si prevede che questo valore scenda ulteriormente a 4,5 µm per lo stacking dei chip N3 e continui a diminuire per le future generazioni di circuiti integrati. Lo stacking di due chip con un passo di bump di dimensioni ridotte rappresenta una sfida significativa, in quanto è necessario ottenere un allineamento di alta precisione sui materiali dielettrici di incollaggio, soprattutto a basse temperature. Inoltre, è necessario un controllo adeguato dei materiali di riempimento del Cu per evitare l'overflow durante il processo di incollaggio. Inoltre, la gestione termica diventa un problema critico per i packages con dimensioni ridotte, il che richiede la considerazione di progetti di packages che consentano una migliore trasmissione del calore e possibili tecnologie di raffreddamento a liquido.

I fattori di crescita

IDTechEx ha identificato quattro aree applicative principali per il packaging avanzato dei semiconduttori: applicazioni/data center per il calcolo ad alte prestazioni (HPC), reti di comunicazione, automobili autonome ed elettronica di consumo. La crescente domanda di elaborazione dei dati è la principale forza trainante della crescita in queste aree applicative. Tuttavia, ogni applicazione ha requisiti specifici che richiedono tecnologie di packaging dei semiconduttori avanzate diverse.

Per le applicazioni HPC/centri dati, la priorità è fornire capacità di elaborazione dati superiori, rendendo le tecnologie 2,5DIC che utilizzano interposer o bridge Si l'opzione preferita, nonostante il loro costo più elevato. Al contrario, l'elettronica di consumo, come gli smartphone o gli smartwatch, si concentra sulla miniaturizzazione e sul costo, e le tecnologie di packaging a base organica sono la scelta migliore.

Nelle comunicazioni 5G e oltre, la sfida principale è la perdita di trasmissione. Per questo motivo, vengono utilizzate tecnologie di packaging avanzate per avvicinare l'antenna al chip IC RF, riducendo al minimo la perdita di trasmissione. L'"Antenna-in-package (AiP)" è attualmente l'opzione più valida per il 5G mmWave, mentre l'"Antenna on chip/wafer (AoP)" è ancora in fase di intenso sviluppo per ridurre i costi.

Per i futuri veicoli autonomi, l'integrazione eterogenea di CPU e altri componenti, come HBM e sistemi di alimentazione affidabili, creerà nuove opportunità per il packaging e l'innovazione dei semiconduttori avanzati.

L'espansione dell'elaborazione dei dati è il fattore di crescita unificante per tutte queste applicazioni. Tuttavia, poiché i requisiti di ciascuna area applicativa sono diversi, le tecnologie avanzate di packaging dei semiconduttori vengono utilizzate per soddisfare esigenze specifiche.

IDTechEx ha pubblicato una nuova ricerca di mercato intitolata "Advanced Semiconductor Packaging 2023-2033". Lo studio esamina le prospettive di mercato, l'analisi dei principali operatori e i più recenti sviluppi nelle tecnologie di packaging avanzato dei semiconduttori. Il rapporto effettua anche un esame completo del mercato dei semiconduttori nel suo complesso. Inoltre, IDTechEx sfrutta la sua esperienza e i suoi anni di ricerca nei settori dei data center, dei veicoli autonomi, del 5G e dell'elettronica di consumo per fornire al lettore una comprensione approfondita del modo in cui il packaging avanzato dei semiconduttori sta influenzando i vari settori e del futuro che potrebbe riservare.