Alla luce dei requisiti computazionali dei paradigmi di intelligenza artificiale, anche le architetture RISC più avanzate, ancorché alimentate da clock a elevata frequenza, non riescono a risolvere le limitazioni imposte dal modello tradizionale della memoria e del suo rapporto con la CPU. Ecco qual potrebbe essere la strada per risolvere questo problema.

La memoria, nell’architettura del computing, ha sempre rappresentato una componente funzionale strategica e nello stesso tempo critica, relativamente a fattori come il consumo di potenza elettrica, al consumo di area di silicio e alle limitazioni delle prestazioni computazionali. L’affermarsi dei nuovi paradigmi computazionali di natura data-driven dell’intelligenza artificiale ha fatto emergere l’inadeguatezza del modello computazionale classico basato sul rapporto master-slave tra unità centrale di elaborazione (CPU) e memoria.

La memoria come semplice contenitore di informazioni rappresenta un “collo di bottiglia” per il flusso di elaborazione, aspetto che aveva indotto all’ottimizzazione dell’architettura della CPU nota come Reduced Instruction Set Computer (RISC).

La legge di Amdahl (Make the common case fast), formulata da Gene Amdhal negli anni Cinquanta, dimostrò che l’efficienza computazionale non dipende dall’hardware, ma dal software (algoritmo o paradigma computazionale).

Quindi soluzioni come il parallelismo esecutivo o l’elevata frequenza di clock, comportavano più problemi (limiti di integrazione, consumo spropositato di potenza elettrica) che vantaggi. La soluzione sta dunque in un diverso modello d’architettura computazionale che l’approccio Application Specific Processor (ASP) dei Digital Signal Processor (DSP), ove l’architettura computazionale era ritagliata sul modello computazionale degli algoritmi di digital signal processing, aveva dimostrato essere quello giusto, situazione questa che aumentava l’efficienza computazionale diminuendo la complessità e la criticità di sistema. Nel caso attuale l’approccio Application Specific può essere declinato come Domain Specific.

La memoria è il sottosistema dell’architettura computazionale su cui si sta concentrando l’attenzione degli sviluppatori di sistemi embedded orientati all’esecuzione dei paradigmi di intelligenza artificiale. Essendo questi “data-driven” e assumendo che il 90% del consumo di potenza elettrica sia determinato dal movimento dei dati, l’orientamento degli sviluppatori delle memorie di nuova generazione è quella di pervenire a soluzioni di memoria di natura Domain Specific.

In-memory Computing

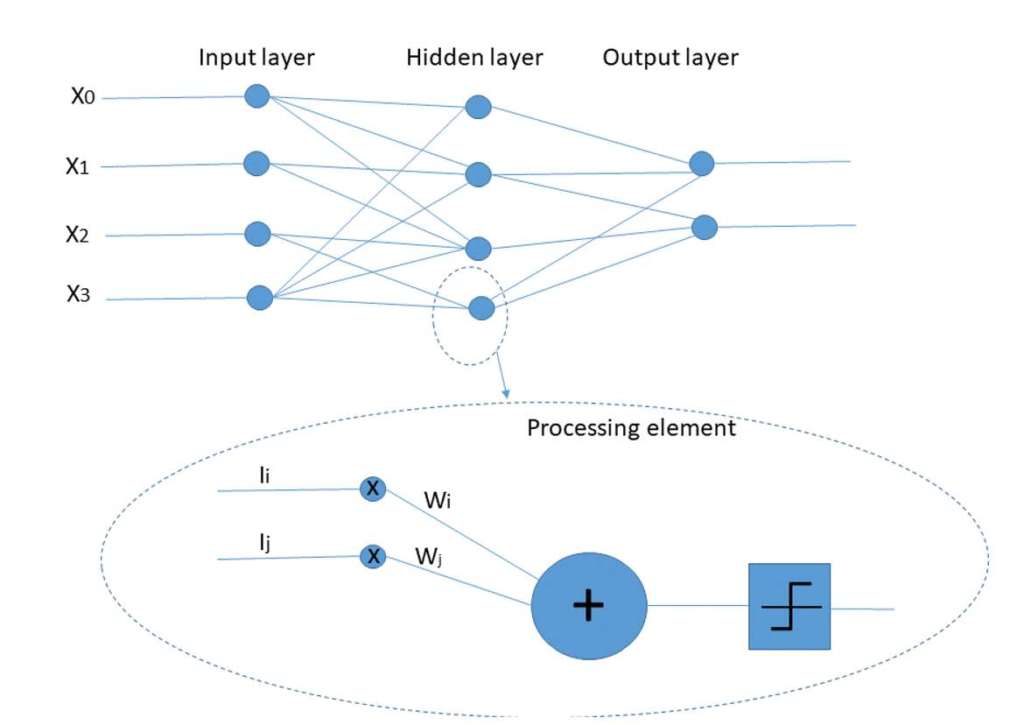

Se si analizza l’architettura computazionale di una rete neurale, si osserva una elevata quantità di nodi (processori elementari) e di interconnessioni tra i nodi.

L’approccio imitativo del modello biologico indurrebbe a pensare che il parallelismo esecutivo (parallel processing) potrebbe essere la soluzione, ma il proliferare degli strati (layer) della rete e quindi dei nodi conseguente all’aumento di efficienza di apprendimento e inferenza porterebbe a una complessità dell’architettura computazionale ingestibile sia dal punto di vista produttivo che applicativo.

Ogni nodo (neurone) esegue un calcolo elementare di moltiplicazione e accumulo per determinare il nuovo dato da propagare verso il nodo successivo, mentre le connessioni (sinapsi) implicano una moltiplicazione tra due dati per determinare il peso della connessione, che rappresenta l’apprendimento.

Queste operazioni implicano la memorizzazione (scrittura) dei dati e un richiamo dalla memoria (lettura) dei dati che determina un elevatissimo flusso di dati tra memoria e CPU che deve eseguire i calcoli, ancorché elementari (somma + moltiplicazione).

La soluzione a questo problema computazionale, mantenendo l’approccio tradizionale è stato quello di integrare la memoria nello stesso chip della CPU (on-chip), con l’ovvia limitazione delle dimensioni limitate rispetto a quella esterna (off-chip).

Una soluzione innovativa è invece quella che si ispira al modello biologico delle reti neurali naturali, cioè integrare il meccanismo computazionale nella memoria a livello di singola cella.

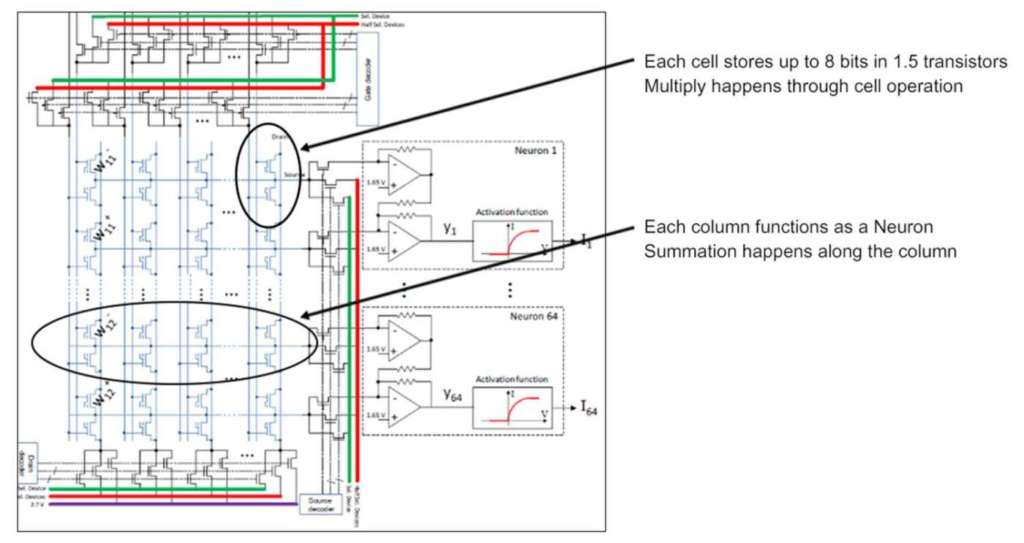

Questo è stato l’approccio che ha portato allo sviluppo della tecnologia memBrain da parte di Silicon Storage Technology (SST), una subsidiary di Microchip Technology.

MemBrain è una soluzione di memoria neuromorfa che utilizzando la tecnologia di memoria flash analogica ottimizza l’esecuzione vettoriale delle operazioni aritmetiche tipiche delle reti neurali artificiali (ANN).

La memoria memBrain memorizza i pesi sinaptici della rete neurale nella floating gate ottenendo un significativo vantaggio nella riduzione della latenza del bus di sistema nella fase di accesso ai dati.

Rispetto alle prestazioni di sistemi come i DSP e le memorie SRAM e DRAM, la riduzione del consumo di potenza elettrica è da 10 a 20 volte e molto significativa è la riduzione del costo di sistema e della latenza in fase inferenziale.

MemBrain di Silicon Storage Technology (SST) è una soluzione di memoria basata sul principio del calcolo In-Memory, che consente di gestire in maniera efficiente l’enorme numero di moltiplicazioni con accumulo (MAC) richiesto dai paradigmi computazionali ANN di natura Deep Learning. I pesi della rete neurale vengono memorizzati nella eFlash ove una cella analogica esegue le operazioni MAC nella stessa memoria, evitando il flusso di entrata ed uscita dei dati necessari per esegure la MAC da parte della CPU.

Dalla memoria digitale alla memoria analogica

La memoria digitale, come tutte le tecnologie digitali microelettroniche integrate subisce i limiti della legge di Moore dovuti al raggiungimento dei limiti fisici di riduzione della densità di integrazione (sub-nanometrica) e della sostenibilità del processo di integrazione sul lungo periodo. Malgrado queste prospettive negative di sviluppo della tecnologia delle memorie digitali, la crescente richiesta di maggiore densità di informazione e di minore consumo energetico da parte dei nuovi paradigmi computazionali sono tali da stimolare la sperimentazione di nuove soluzioni innovative come per esempio lo stacking. Ma la vera innovazione necessita di un drastico cambio di paradigma tecnologico, da digitale ad analogico.

La tecnologia analogica per la memoria è la strada giusta per superare i limiti dello sviluppo delle memorie digitali. È noto che l’informazione principalmente deriva dal mondo fisico, quindi non è di natura discreta e numerica a precisione finita (numeri interi) come assume il modello computazionale Von Neumann, ma di natura continua e numerica a precisione infinita (numeri reali). La memoria analogica richiede un solo dispositivo fisico per memorizzare infinite informazioni a differenza di quella digitale che richiede molteplici dispositivi per memorizzare una singola informazione. Ciò significa che la memoria analogica ha una capacità intrinseca di elevatissima densità di informazione senza richiedere altrettanto elevata densità di integrazione.

Il primo approccio alla implementazione di memorie analogiche è stato imitativo del paradigma delle memorie digitali, cioè di ricerca di un elemento fisico che, ancorché analogico, manifestasse un comportamento digitale (on-off) come per esempio è accaduto per le RAM resistive (ReRAM) ove l’elemento di memorizzazione è la resistenza elettrica utilizzata in due stati opposti (alta resistenza, bassa resistenza): il bit di memoria non è logico ma analogico.

In questi termini l’alternativa analogica a quella digitale non è particolarmente vantaggiosa essendo limitata solo ad una maggiore densità di informazione ed una più elevata densità di integrazione. Il vero vantaggio della soluzione analogica è quello di consentire la memorizzazione di un’intera informazione analogica in un solo elemento fisico e non di un semplice stato logico (on-off). Inoltre, essendo l’informazione memorizzata in forma fisica, è trattabile con le leggi della fisica, quindi processabile all’interno della memoria stessa. Per esempio, nel caso delle ReRAM, ove l’elemento di memoria è la resistenza elettrica, questo componente fisico elettronico è governato notoriamente dalle leggi fondamentali dell’elettronica (Ohm, Kirkoff, ecc.). Quindi la tipica operazione delle memorie (lettura/scrittura di una informazione) diventa per una memoria analogica una operazione computazionale come la MAC (Moltiplicazione e Accumulo), la più ricorrente delle operazioni computazionali degli algoritmi di Digital Signal Processing e dei paradigmi di Intelligenza Artificiale.

Le memorie analogiche aprono dunque un interessantissimo scenario di innovazione dell’architettura di computing in cui la memoria non è solo un contenitore di informazioni, ma anche un sottosistema capace di cooperare con la CPU nel processo di elaborazione dell’informazione in maniera efficace ed efficiente.

Per esempio, se l’elemento fisico di memorizzazione è una resistenza elettrica, la legge di Ohm (V=RI) consente di eseguire la moltiplicazione, la legge di Kirkoff (I=

Ii) consente di eseguire la somma e, in combinazione la moltiplicazione e somma con accumulo (MAC).

I convertitori analogico/digitale (ADC) e digitale/analogico (DAC) consentono di interfacciare in modalità digitale la memoria analogica alla CPU la quale fornisce (scrittura) alla memoria dati in forma digitale binaria che il convertitore DAC trasforma in forma analogica e viceversa (lettura) tramite l’ADC.

L’unico apparente svantaggio della tecnologia analogica e del computing analogico è che le informazioni non sono deterministiche ma sfumate (fuzzy) essendo rappresentate da fenomeni fisici che a loro volta dipendono da altri fenomeni fisici (per esempi la temperatura ambientale). Ma, considerando che i paradigmi computazionali che trarranno vantaggio dall’approccio analogico al computing sono anch’essi di natura sfumata (fuzzy), le memorie analogiche sono la soluzione giusta ai requisiti computazionali del futuro.