Le tecnologie di packaging avanzato dei chip, come packaging 2.5D, packaging 3D e bonding ibrido, svolgono un ruolo cruciale nel migliorare prestazioni ed efficienza dei semiconduttori nelle applicazioni di nuova generazione, basate su AI ed AI generativa. Quest’anno, indicano le stime della società di ricerche Yole Group, la domanda di soluzioni di packaging evolute sta registrando trend in crescita

Una volta ricavati da un wafer di silicio, i chip elettronici, in quanto tali, non sono in grado di funzionare in maniera efficiente e affidabile, fino a quando non vengono racchiusi in un package. Il package li protegge da eventuali danni a livello fisico, ma fornisce anche le connessioni elettriche tra il chip e il circuito stampato (printed circuit board - PCB), dissipando il calore generato dal chip durante il funzionamento.

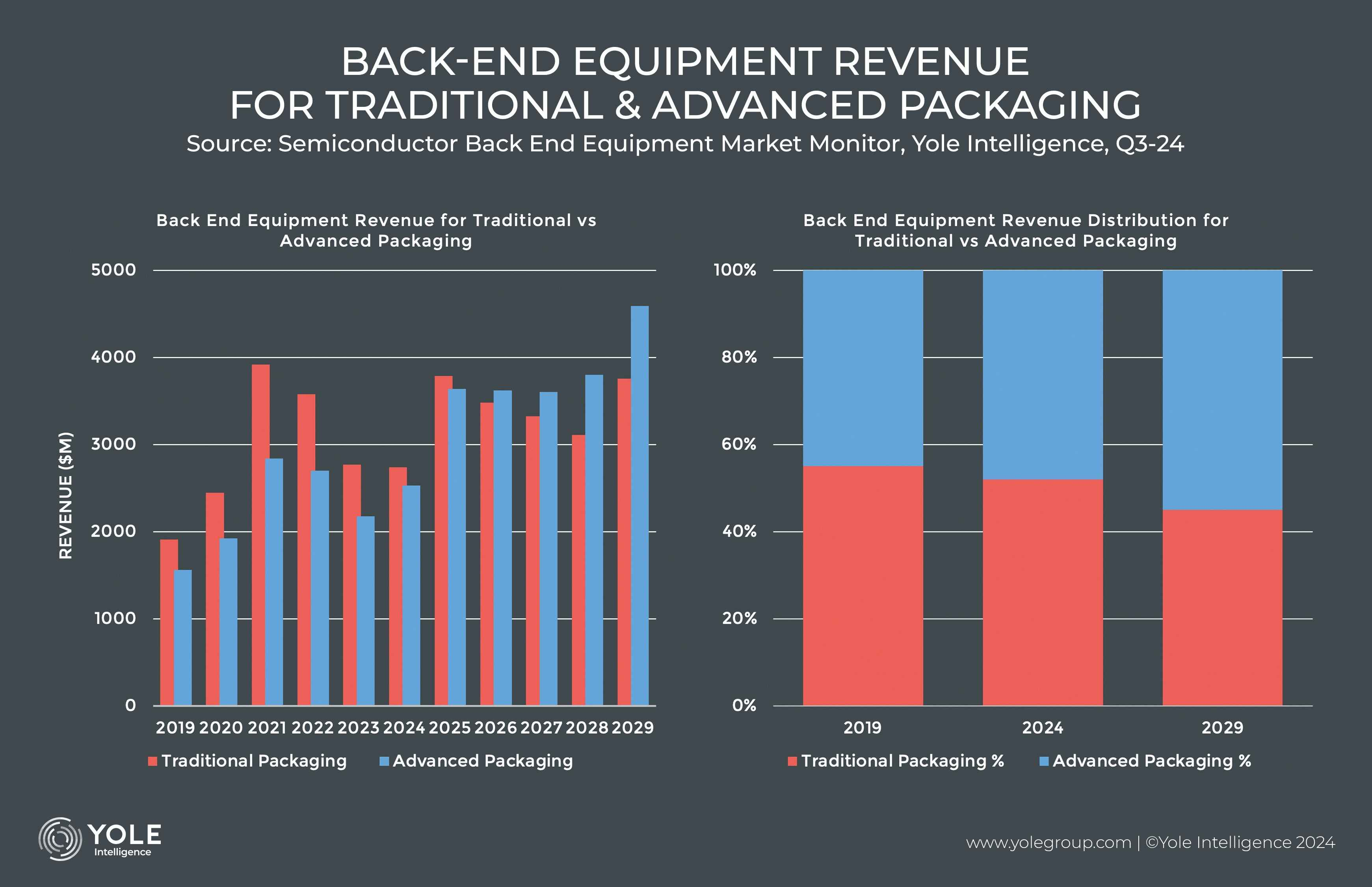

Il packaging dei semiconduttori è un processo cruciale per rendere i chip di silicio integrabili nei dispositivi elettronici, e lo è a maggior ragione oggi, nell’era dell’intelligenza artificiale (AI) e del calcolo ad elevate prestazioni (high performance computing – HPC). AI e HPC stanno in effetti dimostrandosi motori formidabili nell’accelerare con forza, ora e nei prossimi anni, l’espansione e l’evoluzione del comparto delle tecnologie di packaging avanzato dei semiconduttori. Questo ambito tecnologico all’avanguardia, nelle previsioni della società di ricerche e analisi Yole Group, rappresenta il principale fattore di sviluppo per il mercato delle attrezzature back-end, ossia quella categoria di macchinari che consentono di trasformare i chip ricavati dai wafer di silicio in dispositivi e prodotti finali utilizzabili nelle PCB e nei sistemi elettronici.

Un settore, quello delle attrezzature di back-end per i semiconduttori, per il quale gli analisti di Yole Group hanno stimato ricavi per un valore fino a 1,74 miliardi di dollari nel primo trimestre 2025. La domanda di tecnologie di packaging avanzate, tutte legate alla spinta verso l’intelligenza artificiale e l’elaborazione ad alte prestazioni (HPC), rimane resistente. In effetti, indica l’analisi di Yole, tra gli operatori del settore, sia Besi sia ASMPT, due tra i maggiori costruttori e fornitori di strumenti e attrezzature per l’assemblaggio e il packaging dei semiconduttori, hanno registrato notevoli volumi di ordini per equipaggiamenti di packaging 2.5D/3D, nonché per sistemi di bonding ibrido supportati da server AI e memorie ad elevata larghezza di banda (high bandwidth memory - HBM). Queste tecnologie stanno diventando sempre più essenziali per i chip AI di nuova generazione e per le applicazioni fotoniche.

Packaging 2.5D e 3D, caratteristiche e benefici

Nel packaging dei semiconduttori, le espressioni “2.5D” e “3D”, si riferiscono a tecniche avanzate di integrazione dei chip che superano il concetto del convenzionale packaging 2D (2D IC packaging), in cui i chip sono posizionati orizzontalmente, fianco a fianco, su un substrato, una superficie piana, come quella di una PCB. Nel packaging 2D, tutti i chip sono disposti sullo stesso livello, e le interconnessioni tra loro vengono attuate principalmente sulla superficie del substrato. La semplicità di questo approccio, ha reso il packaging 2D una soluzione diffusa, e relativamente poco costosa da produrre. Tuttavia, nel packaging 2D, le distanze di interconnessione possono essere relativamente lunghe in confronto ai metodi più moderni (2.5D, 3D), limitando la velocità di trasferimento dei dati, aumentando la latenza e incrementando il consumo di energia. Inoltre, con questa soluzione, lo spazio non può essere sfruttato in maniera efficiente.

Ciò, nel contesto di continuo aumento della domanda di dispositivi più miniaturizzati e potenti, ha portato gli ingegneri di sistema a studiare necessariamente nuovi approcci, e a concepire la tecnica di packaging 2.5D (2.5D IC packaging), che rappresenta un passo intermedio tra il packaging 2D tradizionale e il packaging 3D. Anche nel packaging 2.5D i chip vengono posizionati fianco a fianco, ma, questa volta, su un “interposer”. L’interposer è in sostanza un substrato intermedio, solitamente in silicio, in grado di fornire interconnessioni ad alta densità tra i chip, creando percorsi più brevi e veloci tra essi. I vantaggi del packaging 2.5D si esprimono soprattutto a livello di prestazioni più elevate, in quanto, grazie all’interposer, le interconnessioni più brevi tra i chip riducono la latenza del segnale e il consumo di energia. Il packaging 2.5D è quindi indicato per applicazioni che richiedono elevate prestazioni, come appunto l’intelligenza artificiale e il calcolo ad alte prestazioni.

Chip in verticale per supportare AI e HPC

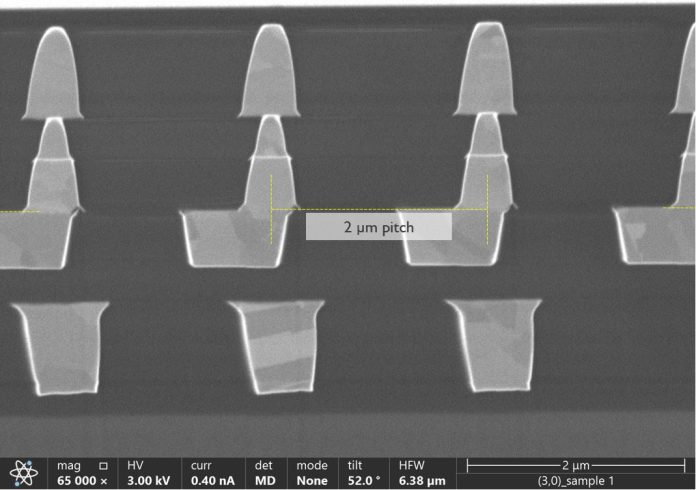

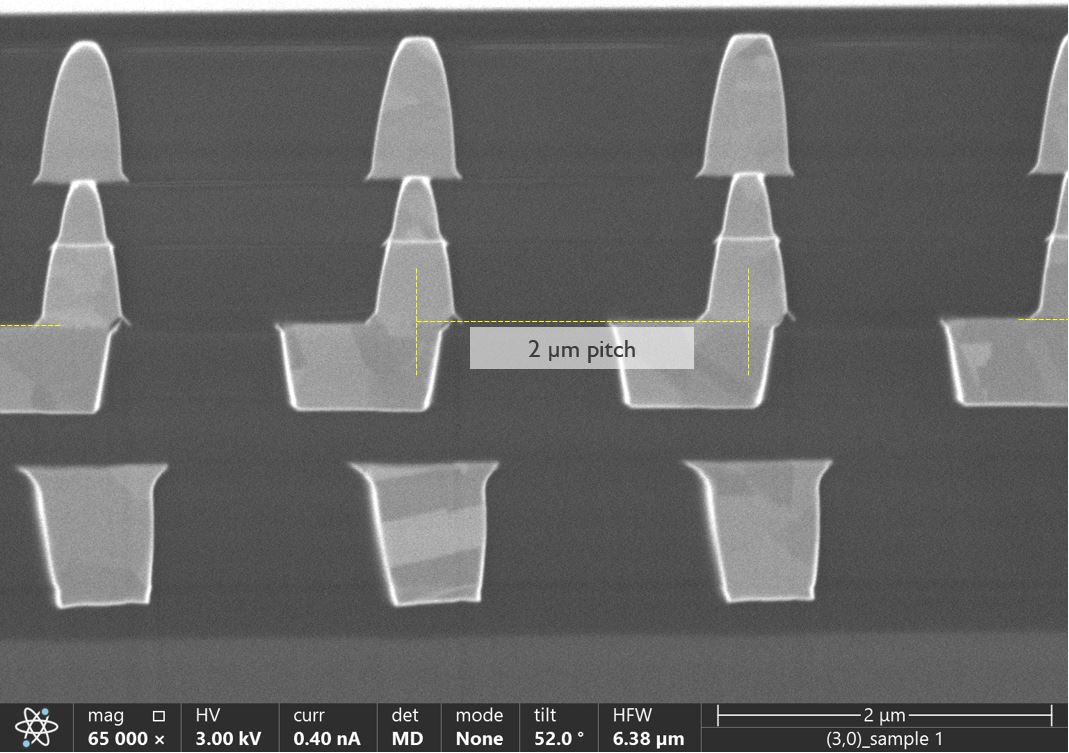

Un’ulteriore evoluzione progettuale rispetto al packaging 2.5D è la tecnica di packaging 3D (3D IC packaging), che nasce dall’esigenza di andare oltre i limiti dell’approccio 2.5D quando il numero di componenti cresce al punto da richiedere nuovo spazio. Il packaging 3D ha l’obiettivo di portare l’integrazione dei chip a un livello ancora maggiore, impilandoli verticalmente, uno sopra l’altro. Questa disposizione dei chip in verticale consente di ottenere una densità di integrazione ancora maggiore e di ridurre ulteriormente le distanze di interconnessione. Le connessioni verticali tra i chip vengono realizzate tramite fori verticali riempiti di materiale conduttivo, simili a sottili pilastri, e chiamati “through-silicon vias” (TSV).

I benefici dell’impilaggio dei chip si traducono in primo luogo in una riduzione dell’ingombro complessivo, che permette di massimizzare la densità di integrazione, e di inserire più funzionalità in uno spazio limitato. Il packaging 3D permette quindi di impilare chip progettati per differenti funzioni, come chip di memoria ad elevata larghezza di banda (HBM), o memoria DRAM (dynamic random access memory) e SRAM (static random access memory), ma anche processori (CPU) e unità di elaborazione grafica (GPU), particolarmente importanti quando si tratta di supportare applicazioni di intelligenza artificiale o di calcolo ad elevate prestazioni (HPC).

Altri chip impilabili possono essere i chip di sensori, come i MEMS (micro electromechanical system) o altri tipi di sensori integrabili per creare sistemi di rilevamento compatti e ad alte prestazioni. Si può integrare chip di circuiti integrati a segnale misto, che combinano circuiti analogici e digitali, e sono utili nel supporto di applicazioni che richiedono l’elaborazione di segnali complessi, o, ancora, sistemi come i chiplet, che sono minuscoli chip specializzati, utilizzabili come mattoncini modulari e componibili per realizzare sistemi più grandi e complessi, come i SoC (system-on-chip). Attraverso il 3D packaging, diventa, in sostanza, possibile impilare chiplet diversi per creare sistemi integrati personalizzati.

Tra i benefici raggiugibili, in primo piano vi sono le performance: le prestazioni del packaging 3D risultano superiori a quelle del packaging 2.5D, con un miglioramento della larghezza di banda, della velocità di comunicazione e dell’efficienza energetica, perché le distanze che i dati devono percorrere sono più brevi. In aggiunta, grazie all’aumento della densità di integrazione, diventa possibile inserire più funzionalità in uno spazio ridotto, e creare dispositivi elettronici più piccoli e compatti. In conclusione, con il packaging 3D, gli ingegneri di sistema hanno l’opportunità di sfruttare la flessibilità di progettazione nell’impilaggio di diverse tipologie di chip, per sviluppare sistemi elettronici ancora più avanzati. Tra le sfide del packaging 3D vi sono tuttavia problemi non sottovalutabili come il surriscaldamento, e la conseguente necessità di dissipazione del calore, che in un sistema elettronico in cui i chip risultano impilati, diventa più difficile da smaltire, in quanto la superficie disponibile per liberarlo è più ridotta. Anche al livello di complessità di fabbricazione, realizzare pile verticali di chip dotati d’interconnessioni affidabili risulta più difficoltoso, rispetto alle tecniche di packaging 2D e 2.5D.

Bonding ibrido per accorciare la distanza tra memoria HBM e processore AI

Bonding ibrido per accorciare la distanza tra memoria HBM e processore AI

Tra le tecnologie avanzate di packaging dei semiconduttori che, come rilevato dagli analisti di Yole Group, stanno registrando un aumento della domanda da parte del mercato, per facilitare lo sviluppo applicazioni di intelligenza artificiale e calcolo ad alte prestazioni, c’è il bonding ibrido. Questa tecnica consente di collegare due o più chip diversi a livello di wafer o die (wafer-to-wafer – W2W, o die-to-wafer - D2W), creando un'interconnessione diretta e ad alta densità. Tale interconnessione, elettrica e meccanica, tra i chip, può essere realizzata adottando metodi differenti, come il bonding diretto rame-rame (Cu-Cu), o il bonding a termocompressione (thermo-compression bonding – TCB).

Ciò differenzia il bonding ibrido rispetto alle tecniche di bonding tradizionali, come il wire bonding o il flip-chip bonding, che, per realizzare l’interconnessione, utilizzano fili di collegamento, oppure minuscole sfere di saldatura (solder bumps). Eliminando fili e bump di saldatura, il bonding ibrido consente di collegare un numero maggiore di chip in uno spazio ridotto, riducendo la distanza di interconnessione e aumentando la velocità di trasferimento dei dati.

Con il bonding ibrido è quindi possibile ridurre la latenza, creare sistemi integrati più piccoli e compatti, e anche ottenere migliori prestazioni elettriche e termiche, in quanto il collegamento diretto tra i chip riduce la resistenza elettrica e migliora la dissipazione del calore. In particolare, il bonding ibrido è concepito per connettere chip di memoria ad elevata larghezza di banda (HBM) e processori AI in maniera estremamente ravvicinata, riducendo la distanza e incrementando in tal modo la rapidità di trasferimento dati.

Potendo essere utilizzato sia per connettere chip fianco a fianco (2.5D), sia impilati verticalmente (3D), il bonding ibrido può rappresentare un'alternativa alla tecnica TSV (through-silicon via), Tuttavia, va aggiunto che i due sistemi di interconnessione possono essere complementari, e quindi coesistere in un dato progetto, con l’obiettivo di riuscire a sfruttare i vantaggi di entrambe le tecnologie.

Esistono poi scenari applicativi specifici in cui bonding ibrido, in virtù delle proprie caratteristiche, si presenta come un’alternativa valida alla tecnica TSV: uno caso progettuale può essere quello dell’integrazione eterogenea. Quando, ad esempio, occorre integrare chiplet caratterizzati da tecnologie differenti (processore, memoria), il bonding ibrido permette di realizzare connessioni dirette e ad alta densità, ottimizzando le prestazioni e i consumi di energia rispetto ai TSV, che potrebbero richiedere interposer complessi, progettati per adattarsi al collegamento di chip differenti, prodotti con tecnologie e materiali disparati.

Advanced packaging: investimenti in aumento tra gli operatori del settore

Per non risultare impreparati a rispondere alla richiesta di tecnologie avanzate di packaging in relazione ai trend innescati da AI e HPC, gli operatori del settore reagiscono. Gli investimenti in capacità di packaging avanzato stanno aumentando in modo significativo, rileva Yole Group: Besi, ad esempio, ha aumentato la spesa in ricerca e sviluppo e la spesa capex (spesa in conto capitale), concentrandosi sull’incremento della capacità di bonding ibrido e TCB per soddisfare l’aumento previsto di tecnologia di packaging evoluta, derivante dalla domanda di applicazioni di intelligenza artificiale. In maniera simile, società come K&S (Kulicke and Soffa) e ASMPT si stanno espandendo attivamente nel settore bonding a termocompressione (TCB) e nei relativi processi “flux-less”, che eliminano la necessità degli agenti chimici tradizionalmente utilizzati per migliorare la saldabilità delle superfici metalliche, in modo da essere pronte per una crescita continua guidata dall’intelligenza artificiale.