La prossima generazione di larghezze di banda per sistemi nei settori aerospaziale e difesa e per test e misurazione sta passando dai decimi/centesimi di megahertz ai multigigahertz di larghezza di banda istantanea. Le tendenze nei radar di tipo phased-array, nei sistemi di test wireless 5G, nella guerra elettronica e negli oscilloscopi digitali stanno spingendo le larghezze di banda sempre più in alto, aumentando notevolmente il numero di canali di un sistema.

Queste tendenze complicano la progettazione della catena di segnale, compresi il convertitore di dati, il clock e l'alimentazione. La selezione del giusto convertitore di dati, la sincronizzazione di più canali e l'ottimizzazione dell'alimentazione sono fondamentali per ottenere la larghezza di banda necessaria su più canali.

Selezione del convertitore di dati

Ogni architettura di sistema ha inizio dal dispositivo che ha l'influenza maggiore sulle prestazioni del sistema: nei sistemi a banda larga, si tratta del convertitore di dati. La sua scelta dipende dalle risposte a queste domande:

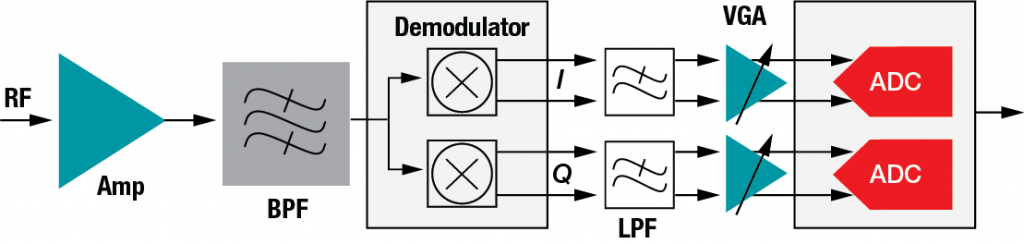

Verrà utilizzata un'architettura a frequenza intermedia (IF) zero/un'architettura mixer complessa (Figura 1)?

- Vantaggi: la larghezza di banda di ingresso del convertitore analogico/digitale (ADC) e le frequenze di campionamento sono inferiori rispetto ad altre architetture ed è possibile semplificare o eliminare il filtraggio.

- Svantaggi: sono necessari due canali ADC per ogni elemento antenna per i percorsi I e Q e l'immagine del mixer può ridurre le prestazioni del sistema.

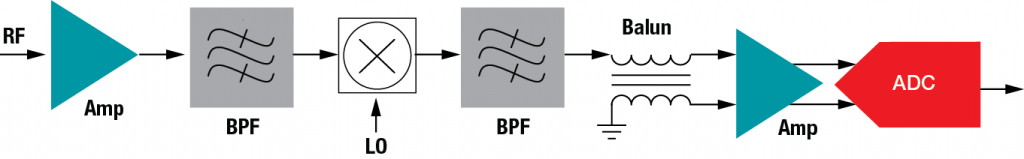

Verrà utilizzato un approccio a eterodina (Figura 2)?

- Vantaggi: è sufficiente un solo canale di conversione dati e la larghezza di banda di ingresso dell'ADC è inferiore al campionamento a radiofrequenza (RF).

- Svantaggi: richiede uno o più mixer, l'immagine del segnale e le armoniche generate complicano il filtraggio ed è difficile regolare la frequenza di interesse. È necessario spostare l'oscillatore locale (LO, Local Oscillator).

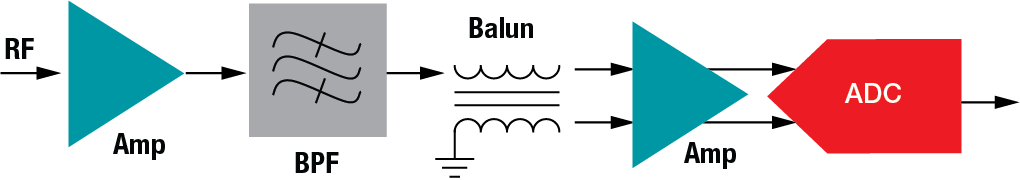

Verrà utilizzato il campionamento RF diretto (Figura 3)?

- Vantaggi: non è necessario un mixer, data la semplificazione della catena del segnale, ed è facile adattare la frequenza in modo digitale utilizzando i convertitori digitali verso il basso DDC (digital down converter) e gli oscillatori a controllo numerico (NCO, numerically controlled oscillator).

- Svantaggi: la più elevata frequenza del segnale deve rientrare nella larghezza di banda di ingresso dell'ADC ed è necessario pianificare la frequenza in modo da ottenere le massime prestazioni.

Figura 3: Tipica architettura di campionamento RF

Qual è il segnale di larghezza di banda più ampio che occorre misurare?

- Come minimo, il convertitore di dati necessita di una frequenza di campionamento pari almeno a 2,5 volte la larghezza di banda istantanea del segnale per il campionamento diretto o 1,25 volte per l'IF zero.

- Per prestazioni ottimali, una frequenza di campionamento pari a circa 10 volte la larghezza di banda istantanea consente di evitare più facilmente le armoniche e le spurie di segnale.

Il pianificatore per frequenza di campionamento RF, filtro analogico e calcolatore Excel DDC di TI può agevolare la pianificazione della frequenza e dei requisiti di filtraggio, mostrando gli effetti della complessa decimazione digitale del segnale.

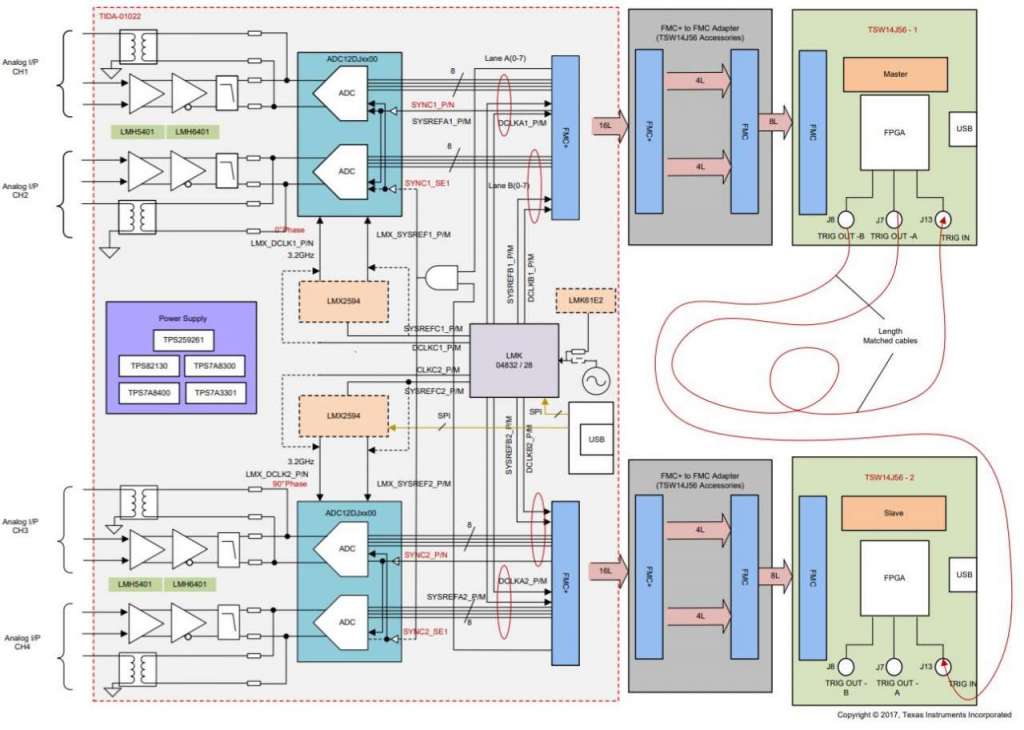

Come accennato in precedenza, i sistemi a banda larga richiedono convertitori ad alta frequenza di campionamento. Ad esempio, un sistema di campionamento RF con una larghezza di banda del segnale di 1 GHz trarrebbe vantaggio da un convertitore di dati con una velocità di conversione di circa 10-GSPS per evitare le armoniche di segnale. Fino a poco tempo fa, il convertitore più veloce di TI era l'ADC12DJ3200, ossia un ADC a 12 bit che opera a 3,2 GSPS per canale in modalità a doppio canale o 6,4 GSPS in modalità a singolo canale. Tuttavia, anche in modalità a singolo canale, esso non raggiunge la velocità desiderata di 10 GSPS. Pertanto, per soddisfare questo requisito, il Progetto di riferimento AFE multicanale a 3,2 GSPS flessibile per DSO, RADAR e sistemi di test wireless 5G, mostrato in Figura 4, combina due ADC12DJ3200 su un'unica scheda.

Questo progetto di riferimento porta flessibilità nel sistema, poiché può operare in modalità a quattro canali e 3,2 GSPS, a doppio canale e 6,4 GSPS o a singolo canale fino a 12,8 GSPS. Il nostro Progetto di riferimento per front-end analogico a 12,8 GSPS per oscilloscopio ad alta velocità e digitalizzatore a banda larga mostra l'interleaving su scheda dei due ADC.

Ora, con l'introduzione del nostro nuovo ADC12DJ5200RF a doppio canale e 5,2 GSPS è possibile ottenere prestazioni e flessibilità ancora superiori per i progetti di prossima generazione. Dal momento che l'ADC12DJ5200RF è compatibile coi pin dell'ADC12DJ3200, è stato possibile modificare rapidamente il progetto di riferimento precedente e proporre ora un Progetto di riferimento a 20,8 GSPS scalabile per digitalizzatori a 12 bit. A 20,8 GSPS, l'intera larghezza di banda in ingresso a 8 GHz del dispositivo può essere digitalizzata in un'unica acquisizione.

Clocking del progetto

Dopo aver scelto il convertitore di dati, è necessario progettare un'architettura di clock. Il clocking di un singolo convertitore di dati è semplice, ma molti sistemi, come il nostro progetto con interleaving, devono sincronizzare più convertitori contemporaneamente. Ad esempio, i sistemi phased-array di grandi dimensioni possono presentare centinaia o migliaia di canali. TI dispone di diversi dispositivi e progetti di riferimento per contribuire a superare questa sfida di progettazione.

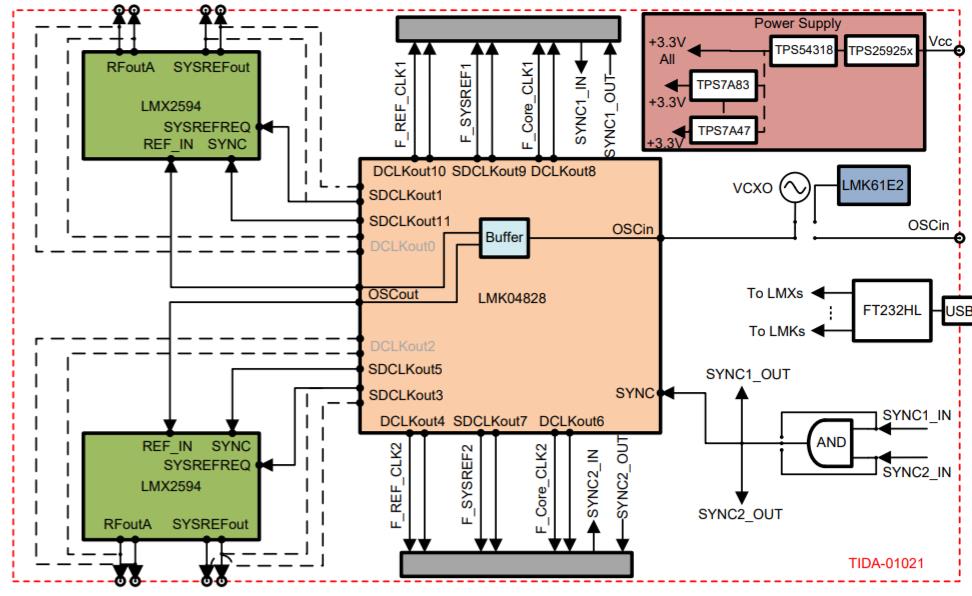

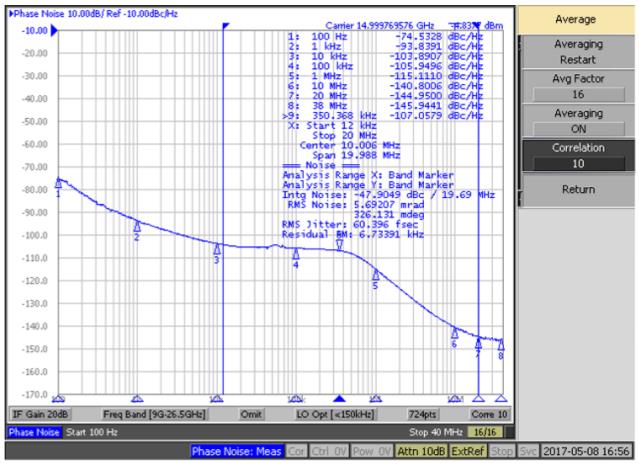

Il nostro Progetto di riferimento per clocking multicanale JESD204B a 15 GHz per DSO, radar e tester wireless 5G è un sottosistema di clock completo. Il progetto, mostrato in Figura 5, comprende svariate opzioni di riferimento del clock, come l'oscillatore programmabile LMK61E2 e il LMK04828, un dispositivo di distribuzione del clock con 14 uscite di clock indipendenti, oltre a due loop/sintetizzatori LMX2594 a blocco di fase, che offrono clock con rumore di fase estremamente basso fino a 15 GHz, come mostrato in Figura 6. Inoltre, il LMX2594 è in grado di generare un clock SYSREF sincrono per convertitori di dati con un'interfaccia JESD204B. Il LMX2594 consente inoltre di sincronizzare la fase dei clock su più dispositivi. Nel progetto di riferimento sono disponibili grafici del rumore di fase a più frequenze, come mostrato nella Figura 6, nonché misurazioni dello sfasamento da canale a canale con sfasamenti inferiori a 10 ps.

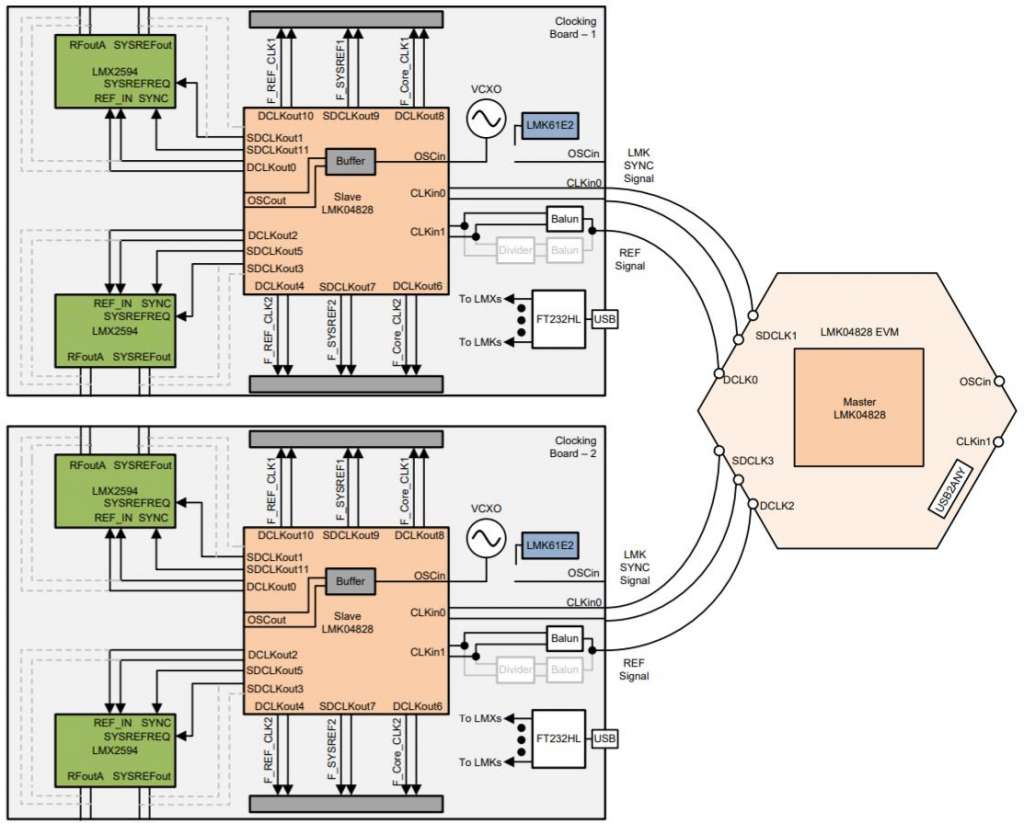

Come configurata, la scheda supporta fino a due convertitori di dati e due FPGA (field-programmable gate array), ma può essere facilmente adattata per sincronizzare fino a sei convertitori e un FPGA. Tuttavia, molti sistemi richiedono un numero di canali notevolmente maggiore. Per queste situazioni, il nostro Progetto di riferimento per la generazione di clock JESD204B ad alto numero di canali per RADAR e tester wireless 5G e il Progetto di riferimento per clock daisy chain JESD204B ad alto numero di canali per RADAR e tester wireless 5G permettono il funzionamento dei nostri clock in una struttura ad albero, mostrata in Figura 7, o in una configurazione daisy chain. Utilizzando queste tecniche, è possibile espandere a migliaia il numero di canali con un degrado minimo delle prestazioni del sistema.

Energia al progetto

Una volta risolta la questione dell'architettura di clock, la sfida successiva è dare energia al progetto. I convertitori di dati e i clock possono essere sensibili al rumore di commutazione dei convertitori CC/CC, pertanto la maggior parte dei progettisti di alimentazione abbina al convertitore CC/CC un regolatore a basso rumore e basso dropout (LDO, low-dropout regulator). Tuttavia, avendo cura nel layout e nel filtraggio, gli LDO spesso non sono necessari su molti sistemi di alimentazione.

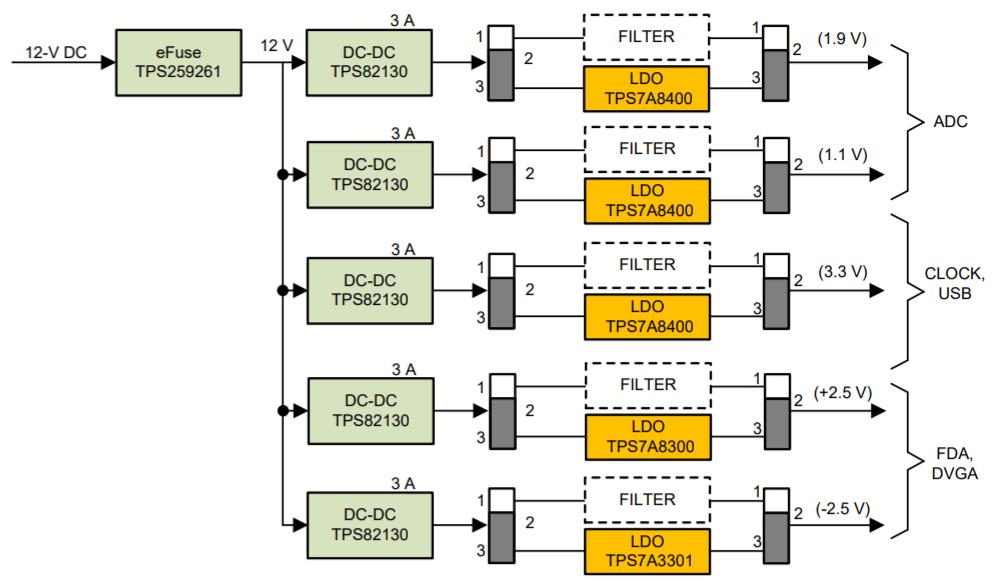

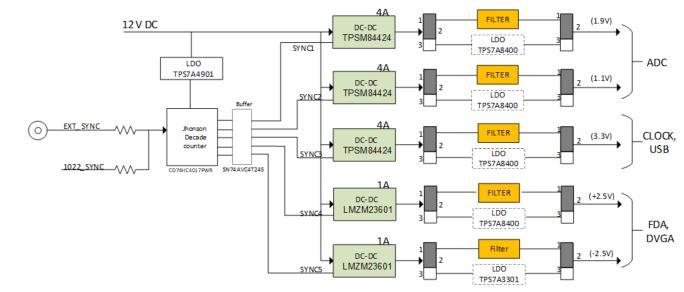

Il progetto di riferimento per front-end analogico multicanale a 3,2 GSPS citato in precedenza dispone di un alimentatore completo, inclusi i regolatori CC/CC e gli LDO, come mostrato nella Figura 8. Gli LDO in questo progetto possono essere bypassati con filtri per testare quali alimentazioni sono più sensibili al rumore di commutazione. I nostri test hanno confermato che non vi è alcun impatto sulle prestazioni del progetto bypassando gli LDO, il che offre anche il vantaggio aggiuntivo di una maggiore efficienza dell'alimentatore.

La scheda contiene inoltre una serie di pin di intestazione nella parte superiore che consentono di bypassare la soluzione ad alimentazione integrata con un nuovo progetto, come il nostro Progetto di riferimento per alimentatore a basso rumore per massimizzare le prestazioni nei sistemi di acquisizione dati a 12,8 GSPS. Questo progetto di riferimento, mostrato nella Figura 9, consente di sincronizzare tutti i regolatori CC/CC con un clock master, facilitando il filtraggio del rumore di commutazione del convertitore. Inoltre è possibile spostare la fase del clock su ciascun convertitore in modo che tutti i convertitori non commutino contemporaneamente, riducendo quindi l'energia di commutazione totale. Infine, i convertitori CC/CC nel progetto di riferimento sono più efficienti, riducendo la perdita di potenza totale della scheda. Come nel progetto originale, è ancora possibile bypassare gli LDO.

Come appare evidente, la scelta del convertitore di dati corretto non è che una delle tante sfide da affrontare. Dopo aver fatto tale scelta, è fondamentale scegliere i migliori progetti per il clock e per l'alimentatore, al fine di non degradare le prestazioni di un costoso convertitore di dati.

Risorse supplementari

Guardate il video di formazione: Ottimizzazione delle prestazioni del ricevitore ADC per campionamento RF con il calcolatore di pianificazione della frequenza e della frequenza di campionamento.

Scoprite la gamma completa di ADC ad alta velocità e di convertitori digitale/analogico di TI.