Gli Lcd si trovano oggi su elettrodomestici come frigoriferi, lavatrici e asciugatrici con lo scopo di migliorare le capacità di controllo da parte dell'utilizzatore. Molto probabilmente a causa della proliferazione degli smartphone e delle interfacce utente di tipo grafico, i display Lcd sono divenuti un prerequisito per il successo di un prodotto, dal momento che i clienti si aspettano funzionalità intuitive, affidabili e visivamente accattivanti. Per esempio, le interfacce grafiche degli elettrodomestici sono state tra le principali novità che hanno caratterizzato l'ultimo decennio. Le tecnologie avanzate dei display ne hanno trasformato il layout da statico a dinamico, e il design adattativo ha aggiunto paradigmi complessi al sistema. Mettere in pratica un design grafico dinamico è un lavoro che consuma grandi quantità di dati e di potenza di calcolo, fatto che aumenta la complessità e i costi dell'intero sistema. La qualità e la reattività dell'interfaccia grafica sono rappresentative del prodotto finale poiché restituiscono all'utente la prima impressione del prodotto stesso. Le interfacce grafiche di alta qualità consumano tantissime risorse e sono implementate su processori molto costosi, quando invece i dispositivi destinati agli apparati industriali e agli elettrodomestici bianchi presentano fortissimi vincoli in termini di costo. Un utilizzo corretto delle risorse interne del processore, un buon allineamento tra i differenti moduli software grafici e un accesso prioritario da parte del controller Lcd al bus di sistema sono elementi essenziali per le prestazioni del sistema.

Requisiti di memoria e ottimizzazione della bandwidth del bus

Le dimensioni e i costi dei prodotti Hmi hanno una ricaduta significativa sulla tipologia di Hmi che può essere implementata. Per prima cosa, la maggior parte delle applicazioni Hmi è basata su Mpu che necessitano di memoria esterna su cui vengono conservati i programmi e i dati. I programmi si trovano normalmente su memoria non volatile come Nand o serial Flash. Al momento del boot, il codice del programma viene trasferito su una memoria Dram all'interno della quale viene eseguito. La memoria Dram viene impiegata anche per conservare i frame buffer necessari al rinfresco del display. Persino un formato compatto come Qvga da 320 x 240 punti per 16 colori ha bisogno di 150 KB di Sram, un valore elevato da dedicare sulla Sram interna. L'utilizzo di schermi di dimensioni superiori a 4,3" richiede ancora più memoria che va a incidere sulla distinta base del prodotto. Il ricorso a memoria esterna fornisce inoltre ai progettisti la possibilità di scalare i costi della memoria a seconda delle loro esigenze e quindi scegliere il fornitore preferito. Per mantenere l'immagine, gli schermi Lcd devono essere periodicamente sottoposti a un rinfresco video. Il controller Lcd preleva i dati da locazioni di memoria sequenziali a partire dall'indirizzo di inizio programmato nei registri del controller Lcd stesso. Il rinfresco viene lanciato da un trigger software o automaticamente in background via Dma e consuma una porzione molto significativa della bandwidth di sistema disponibile. La bandwidth di memoria totale minima richiesta per questa procedura può essere calcolata secondo la seguente equazione:

Bandwidthdimemoria=RisoluzioneorizzontalexRisoluzioneverticalexBppmemoriaxFrequenzadirinfresco

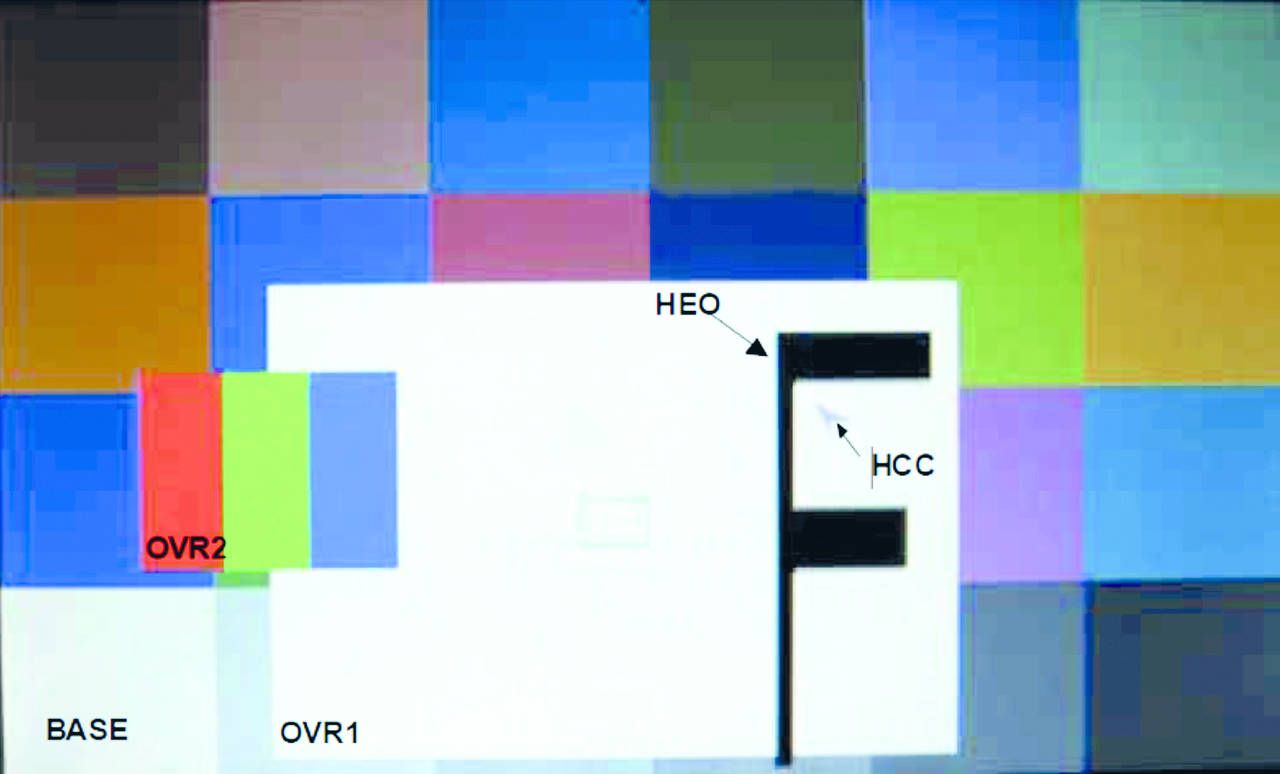

Nel design delle interfacce grafiche dinamiche occorrono ulteriori frame buffer. Per esempio, la maggior parte delle implementazioni di software grafico impiega due frame buffer separati per poterne aggiornare uno mentre l'altro è impegnato nel rinfresco dello schermo Lcd. Software grafici sofisticati prevedono anche ulteriori funzionalità, come ad esempio il multilayer, con l'effetto di estendere i requisiti di bandwidth di memoria dell'interfaccia grafica. Tornando all'equazione appena vista, le performance dell'applicazione sono direttamente correlate alla bandwidth di memoria del controller Lcd. I processori basati su Arm Cortex A5 sono dotati di un paio di caratteristiche che ottimizzano l'accesso alla memoria da parte del controller Lcd senza compromettere le prestazioni del sistema. Il modulo Lcd integra un modulo Dma Engine Address Generation che esegue il prefetch dei dati e richiede l'accesso all'interfaccia Ahb. Il controller Dma legge l'immagine attraverso la doppia interfaccia master Ahb a 64 bit, progettata in modo da migliorare la bandwidth di accesso alla memoria. Nel caso del base layer, dell'over layer e del layer Heo, gli utenti possono selezionare l'interfaccia master Ahb adatta alle proprie applicazioni mediante un apposito campo nei registri di configurazione di ciascun layer. Questa selezione permette ai programmatori di bilanciare il carico di accesso alla memoria nei design multilayer. Oltre a questo, il bus Ahb è connesso alla memoria esterna attraverso un controller Ddr_Sdram multiporta con otto interfacce AHB slave. Tutte le otto porte Ahb indipendenti sono di tipo interleaved per massimizzare la bandwidth di memoria e minimizzare i tempi di latenza dovuti al protocollo Ddr. Il controller Ddr estende le capacità di memoria del chip fornendo l'interfaccia verso il dispositivo Ddr-Sdram esterno a 16 o 32 bit. Dal momento che i frame buffer dedicati al rinfresco dello schermo Lcd hanno bisogno di più memoria rispetto a quella disponibile a bordo del chip, essi sono allocati all'interno della memoria Ddr esterna. La gestione di tutti gli accessi al sistema e ai frame buffer in parallelo e la flessibilità fornita dalle otto porte Ahb indipendenti del controller Ddr massimizzano la bandwidth di memoria del sistema complessivo e ne minimizzano i tempi di latenza. I vantaggi del sistema di bus integrato nella famiglia SAMA5DX di Atmel hanno un notevole impatto sulla bandwidth delle applicazioni di interfaccia utente. Come si può notare nella tabella che segue, la matrice bus H64MX gestisce 10 master. Il circuito LcdC Dma dispone di due porte master verso il bus direttamente collegate alle porte Ddr, potendo effettuare l'accesso Ddr in maniera concorrente rispetto alle altre attività sul bus degli altri 8 master e degli 11 ulteriori slave così da sfruttare al meglio la bandwidth del bus da 64 bit clockato con un Mck di 176 MHz. Il controller Ddr presente sui modelli delle famiglie SAMA5Dx supporta operazioni di lettura o scrittura in burst di otto locazioni di memoria; questo permette al bus dei comandi e degli indirizzi di anticipare il comando successivo così da ridurre i tempi di latenza. I burst rappresentano il modo più efficiente per trasferire dati: ricorrendo a questo accorgimento lo schermo Lcd riceve i dati più velocemente liberando il bus esterno per l'utilizzo da parte di altri master. Abilitare la modalità burst è necessario per ottenere i livelli di throughput nella lettura della Ram. Il controller Ddr, inoltre, tiene traccia della riga attiva di ciascun banco massimizzando le performance dell'accesso alla memoria Ddr evitando di accedere contemporaneamente a più righe. Il controller Lcd offre la possibilità di ricorrere a tecniche multilayer per migliorare il design delle interfacce utente. Per poter essere visualizzato sul display Lcd, ciascun layer ha bisogno di bandwidth di memoria supplementare. La figura fornisce un esempio della configurazione Lcd che mette in evidenza l'utilizzo dei diversi layer di differenti dimensioni che vengono visualizzati su uno schermo da 800 x 480 punti. La somma delle bandwidth utilizzate dai vari layer raggiunge un utilizzo totale del 30% della bandwidth di memoria Ddr2 disponibile. L'utente deve configurare attentamente ciascun layer per ottenere le prestazioni migliori all'interno del sistema complessivo.

Accelerazione grafica con Dsp Arm e funzionalità Lcd avanzate

La richiesta di funzionalità grafiche 2D/3D sta rapidamente aumentando allo scopo di poter implementare interfacce utente più accattivanti. Le funzioni grafiche richiedono parecchi calcoli e spesso aumentano il carico sopportato dalle risorse di sistema. Le interfacce utente sono oggi basate su grafica 2D, 2,5D o persino 3D, e ciascuna tecnica visuale richiede il proprio livello di potenza di calcolo, bandwidth e memoria. Una delle alternative più efficaci è quella di utilizzare l'accelerazione grafica via hardware per aumentare le performance delle funzioni 2D/3D. Tuttavia, le limitazioni fisiche come il livello di alimentazione dell'acceleratore grafico e il fatto che esso dovrebbe risiedere su un unico chip a fianco di altri blocchi come la Cpu hanno la conseguenza di incrementare i costi dei processori dotati di acceleratore grafico integrato. I progettisti di processori destinati alle applicazioni Hmi devono spesso affrontare un compromesso tra prestazioni e costo totale del sistema. Il controller Lcd SAMA5Dx di Atmel supporta funzioni di accelerazione hardware della grafica 2D con tecniche complesse come alpha blending, rotazione di 90°, 180° e 270° con ribaltamento verticale e orizzontale, ridimensionamento con rapporti non interi fino a 1280x720 pixel, conversione colore da YUV (Y’CbCr) a Rgb e chroma upsampling da YUV 4:2:0 a YUV 4:4:4. Il core Arm Cortex A5 integra inoltre un coprocessore Neon con un'architettura Simd che Arm ha progettato per accelerare gli algoritmi multimediali e di signal processing compresa la grafica 2D/3D. La famiglia di processori SAMA5Dx sfrutta l'architettura Neon e una cache L2 da 128 KByte per accelerare le operazioni grafiche senza aumentare il costo del sistema attraverso l'aggiunta di acceleratori. La maggior parte delle implementazioni di software grafico 2D/3D è basata su librerie come DirectFB che forniscono accelerazione grafica; queste funzioni integrano un layer di astrazione hardware per le operazioni grafiche che potrebbero essere supportate dall'acceleratore hardware e che per funzionare utilizzano chiamate tipo OpenGL, o che potrebbero essere implementate in software. Un'implementazione DirectFB ottimizzata su Neon è stata integrata e collaudata sul SAMA5D4. I dati che seguono dimostrano il miglioramento di DirectFB con abilitati Neon e la cache L2 per i calcoli a 16 e 32 bit.