Sfide di progettazione e layout associate alla progettazione elettronica dei phased array planari, in particolare su un front-end RF contenente amplificatori di potenza (PA), amplificatori a basso rumore (LNA) e beamformer. Ne parlano gli specialisti di Analog Devices.

Vengono discussi i segnali e il timing coinvolti nel controllo del bias di PA e LNA, nella commutazione tra trasmissione e ricezione, nel caricamento della memoria e nell'avanzamento del beam. Il layout del PCB è incentrato su una singola cella, costituita da un beamformer circondato da quattro moduli di trasmissione/ricezione (TR). Sono presentate le sfide di gestione termica, tra cui la dissipazione del calore sul lato del componente e la progettazione della cavità del dissipatore di calore con assorbitori RF per evitare oscillazioni. Viene descritto il progetto di gestione dell'alimentazione per il front-end RF, comprese le ramificazioni di alimentazione e la specifica sequenza di bias necessaria per evitare danni al PA.

I sistemi phased array planari bidimensionali, in cui i circuiti RF e gli elementi dell'antenna si trovano sui lati opposti dello stesso PCB, offrono un vantaggio significativo in termini di dimensioni rispetto alle strutture tridimensionali a lama. Ma questo vantaggio dimensionale comporta problemi di layout, di gestione dell'alimentazione e termici. Tutto ciò si aggiunge alle tradizionali sfide di progettazione del timing associate ai sistemi radar. Questo articolo analizza come alcune sfide possano essere affrontate studiando attentamente funzionalità e interfacce dei dispositivi, un'accurata disposizione sul PCB, che massimizzi l'uso del limitato spazio disponibile, nuove tecniche di dissipazione del calore e gestione dell'alimentazione ben pianificata, che garantisca un'accensione e uno spegnimento sicuri con un corretto sequencing. (Figura 1)

I sistemi radar phased array sono costituiti da numerose sezioni, tra cui il software e l'FPGA, gli ADC e i DAC, gli upconverter/downconverter, i circuiti RF e di beamforming e gli elementi dell'antenna phased array. Questo articolo si incentra sul front-end RF e sulla formazione del beam.

Progettazione e timing del sistema radar

Nei radar moderni, i blocchi di fase e ampiezza variabili sono consolidati in un circuito integrato beamformer (BFIC), dove ogni BFIC contiene diversi blocchi di ampiezza e fase variabili. Inoltre, il PA, l'LNA e lo switch di trasmissione/ricezione possono essere integrati in un singolo modulo TR ed essere progettati in modo ottimale per funzionare direttamente con il BFIC.

Un radar a impulsi monostatico presenta due caratteristiche di timing critiche: la durata dell'impulso di trasmissione (τ) e il tempo di ripetizione dell'impulso (PRT), ovvero l'intervallo tra gli impulsi di trasmissione. I radar moderni hanno una durata degli impulsi di trasmissione compresa tra 10 e 100 μs. Tuttavia, alcune applicazioni prevedono durate fino a 500 ns. I tempi di salita e discesa tipici sono compresi tra 500 ns e 1 μs e i duty cycle di trasmissione sono compresi tra l'1% e il 20%. Il timing tipico dei radar a impulsi è illustrato nella Figura 2.

Parametri radar come il campo di misura minimo (RMIN) o il campo cieco, la risoluzione del campo e gli hit per scansione sono direttamente proporzionali a τ e PRT. Il campo di misura minimo è anche direttamente proporzionale al tempo di switch da trasmissione a ricezione:

La riduzione al minimo del tempo di switch da trasmissione a ricezione è fondamentale nei radar di ricerca, dove i bersagli possono essere relativamente vicini al trasmettitore.

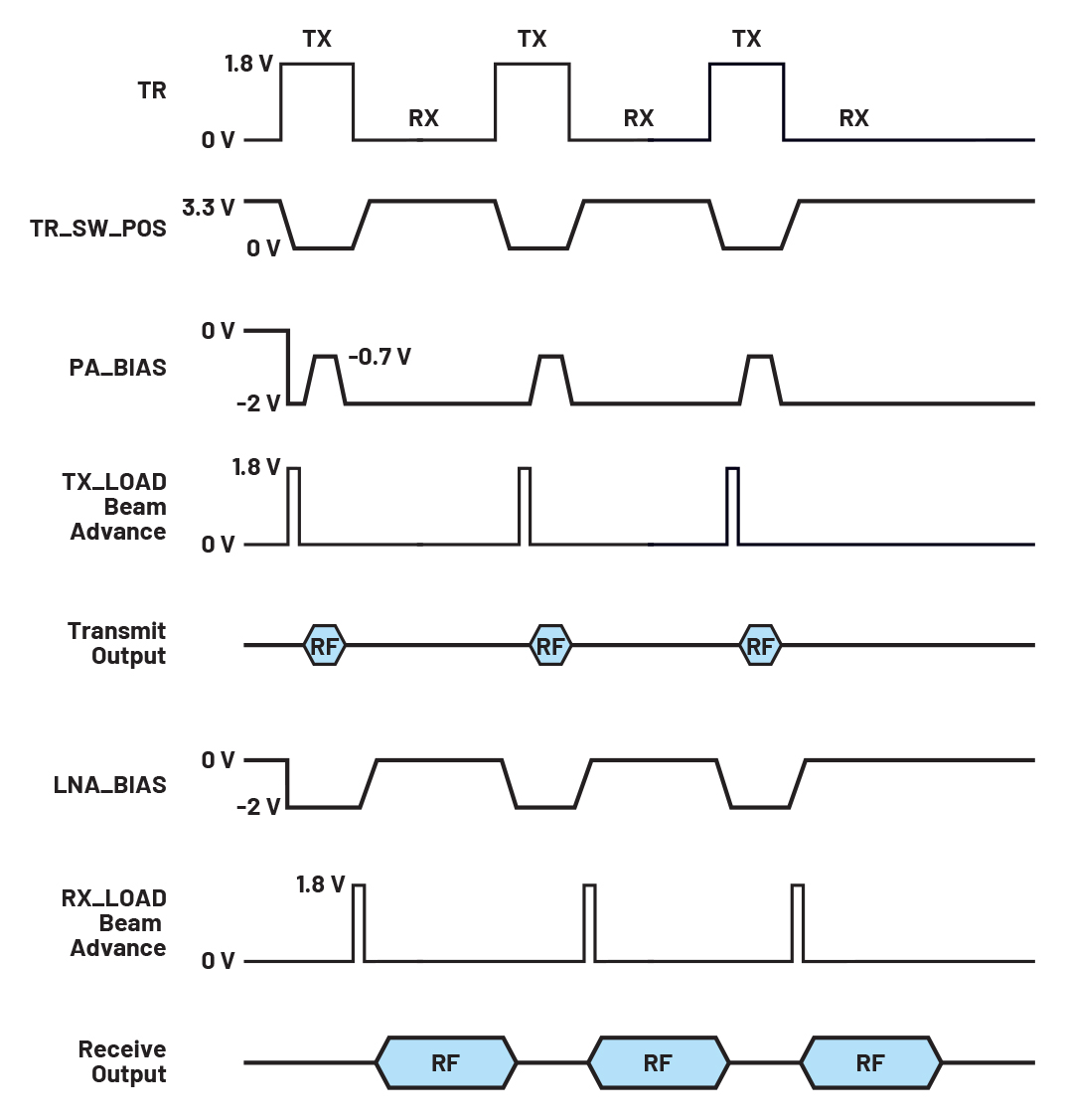

I radar phased array monostatici sono spesso sistemi half-duplex. Il passaggio da trasmissione a ricezione è realizzato con diversi segnali di controllo che devono essere sequenziati contestualmente. Questi segnali di controllo svolgono le seguenti funzioni:

- attivare lo switch trasmissione/ricezione;

- abilitare e disabilitare il PA;

- abilitare e disabilitare l’LNA;

- abilitare e disabilitare i percorsi di trasmissione e ricezione del

Inoltre, quando la direzione del beam cambia, è necessario caricare nuovi pesi di beam nei blocchi di ampiezza e fase variabili. Se si dispone di una memoria locale su chip per memorizzare più serie di questi pesi, l'avanzamento del beam può essere attivato con un singolo impulso di un pin di controllo e senza scritture SPI. Un esempio di sequencing e di livelli di tensione di questi controlli è mostrato nella Figura 3.

La Figura 4 mostra un esempio di interfacciamento e controllo del mondo reale. Un singolo canale del BFIC ADAR1000 viene collegato a un singolo modulo TR ADTR1107. I due chip presentano un unico segnale di controllo di trasmissione/ricezione che va all'ADAR1000 tramite il pin TR. Questo pin controlla a sua volta il bias del PA, il bias dell'LNA e l'interruttore di trasmissione/ricezione sul modulo TR ADTR1107 e controlla l'abilitazione/disabilitazione dei percorsi interni di trasmissione e ricezione del beamforming dell'ADAR1000. L'integrazione del controllo di trasmissione/ricezione non solo riduce la complessità del layout della scheda, eliminando numerose linee di controllo, ma consente anche tempi di switch rapidi tra trasmissione e ricezione, in modo che parametri come il campo di misura minimo siano i più brevi possibili.

Memoria del beam

Una soluzione discreta di beamforming deve applicare i pesi del beam da un chip di memoria ai diversi blocchi di ampiezza e di fase variabili. La maggiore complessità del routing e il tempo necessario per eseguire un avanzamento del beam sono i due principali svantaggi della progettazione di sistemi discreti. I moderni radar phased array che utilizzano BFIC integrati come l'ADAR1000 hanno una memoria on-chip che richiede un singolo impulso di carico e pochi cicli di clock aggiuntivi per l'avanzamento del beam. I BFIC più recenti, come ADAR3000 e ADAR3001, hanno ridotto questa operazione a un singolo impulso di memoria.

Nell'esempio illustrato nella Figura 4, il BFIC ADAR1000 dispone di due posizioni on-chip in grado di memorizzare i dati del beam: registri e memoria ad accesso casuale (RAM). L'utilizzo di entrambi i tipi di memoria per la memorizzazione dei dati del beam presenta vantaggi e svantaggi. Entrambi i tipi sono limitati dalla velocità massima del clock SPI di 25 MHz durante la scrittura e la lettura dei dati del beam.

L'approvvigionamento dei dati del beam dai registri ha il vantaggio di disporre di dati sufficienti per una sola posizione del beam e di memorizzarli direttamente nei registri; non è quindi necessario azionare il sequencer o eseguire il fetching della memoria. Questa modalità di funzionamento può essere importante nelle applicazioni in cui l'utente non conosce a priori il prossimo angolo di orientamento del beam e quindi è necessario implementare uno schema di scrittura al volo dei nuovi dati del beam per ogni nuovo angolo di orientamento. Lo svantaggio dell'uso dei registri è il tempo necessario per inserire la posizione di ogni nuovo beam, limitato dalla velocità massima di clock di 25 MHz. A questa velocità di clock, sono necessari 4,16 μs per caricare una posizione del beam in ricezione o in trasmissione. Inoltre, è necessario un comando di caricamento rapido per istruire il chip a utilizzare i nuovi dati del beam nei registri, poiché l'ADAR1000 utilizza registri dual rank.

L'approvvigionamento dei dati dalla RAM è vantaggioso se il sistema conosce a priori gli angoli di orientamento del beam e può quindi registrare tutti i dati di posizione del beam necessari prima del funzionamento attivo del sistema. Le applicazioni che utilizzano una scansione raster, come i radar meteorologici e di ricerca, possono trarre vantaggio dalla memorizzazione delle posizioni dei beam nella RAM. Il tempo necessario per inserire ogni posizione del beam nella RAM è lo stesso dei registri, ma poiché questa operazione viene normalmente eseguita prima del funzionamento attivo, per attivare una nuova posizione del beam con l'ADAR1000 sono sufficienti 6 cicli di clock, più un comando di caricamento. Questa operazione richiede appena 320 ns.

Partizione della RAM

Se si utilizza la RAM per generare i dati della posizione del beam, è possibile utilizzare il partizionamento di questa RAM per aggiornarne una sezione mentre il controllore radar accede all'altra. Solo una sezione viene attivata per i dati di posizione del beam, mentre i nuovi dati del beam vengono scritti nelle altre sezioni. Ciò è possibile grazie all'uso dei puntatori di start e stop della RAM dell'ADAR1000, che consentono al sequencer di avviarsi e fermarsi in qualsiasi posizione arbitraria del beam nella RAM.

Un semplice esempio consiste nel dividere la RAM in due sezioni: La Sezione 1 contiene le posizioni del beam da 0 a 60, mentre la Sezione 2 contiene le posizioni del beam da 61 a 120. Inizialmente, i valori dei puntatori di start e di stop sono impostati rispettivamente su 0 e 60. Anche i dati del beam vengono inseriti nelle posizioni da 0 a 60 e viene caricata la posizione 0 del beam. L'avanzamento del beam dalle posizioni 0 a 60 avviene più volte (il sequencer si riavvia e carica la posizione iniziale del beam dopo quella di arresto). Tra gli avanzamenti del beam della Sezione 1, vengono caricati i dati del beam della Sezione 2.

Quando si è pronti a passare dai dati della Sezione 1 a quelli della Sezione 2, è necessario impostare un nuovo valore del puntatore di stop. Per garantire una transizione fluida tra le posizioni del fascio 60 e 61, il nuovo valore del puntatore di stop deve essere scritto quando il sequencer si trova nella posizione del fascio 58 o prima. Nella prima sequenza attraverso le posizioni del fascio da 61 a 120, è necessario scrivere un nuovo valore del puntatore di avvio. Questo nuovo valore deve essere impostato quando il sequencer si trova nella posizione del fascio 118 o prima, altrimenti la transizione alla posizione del fascio 61 non sarà fluida. In generale, i nuovi dati del beam o i nuovi valori del puntatore devono essere inseriti con un anticipo di due posizioni di beam rispetto alla posizione attiva del beam stesso.

La scrittura di nuovi dati e il successivo ritorno alla memoria della Sezione 1 possono essere ottenuti con la stessa tecnica descritta nell'esempio precedente.

Layout del PCB

I sistemi radar Phased Array possono variare per numero di elementi e dimensioni, da un sub-array di prototipazione 2 × 2 ad array con 256, 512 o addirittura 1024 elementi. Il layout dell'array può essere semplificato fino a un'unità di cella, in genere collegata a quattro elementi. La dimensione primaria della cella dipende dalla spaziatura del reticolo, di solito λ/2, in modo che non appaiano lobi di reticolo per il pilotaggio del beam fino all'orizzonte dell'apertura. A volte si sceglie una distanza tra i reticoli leggermente superiore a λ/2 per ottenere un guadagno d'antenna maggiore e larghezze di beam più sottili; tuttavia, ciò riduce l'intervallo di beam steering che non presenta lobi di reticolo. La posizione dei moduli BFIC e TR è solitamente vincolata alla spaziatura del reticolo.

Layout di cella

La Figura 5 mostra un esempio di layout di cella su una scheda di sistema phased array planare di Analog Devices. Si tratta di un BFIC a quattro canali con quattro moduli TR che circondano il BFIC.

L'obiettivo del layout della cella era quello di ottenere una distanza tra i reticoli di 15 mm (λ/2 a 10 GHz) e di far corrispondere in lunghezza le linee di trasmissione e ricezione RF che vanno dal BFIC ai quattro moduli TR. La frequenza di 10 GHz è stata scelta per λ/2 in quanto si trova al centro della banda X, dove operano molti sistemi radar e alcuni sistemi di comunicazione satellitare. La corrispondenza della lunghezza delle linee di interconnessione di trasmissione e ricezione tra il BFIC e il modulo TR riduce l'onere della calibrazione.

L'interfaccia glueless tra il BFIC e i quattro moduli TR consente di non avere quasi nessun componente esterno sulle linee di trasmissione, ricezione o accoppiatore che vanno ai rilevatori di potenza. Ciò rende efficiente il routing del layout, come illustrato nella Figura 5. L'interfaccia glueless, insieme ai chip dei moduli TR orientati a 45° fuori asse rispetto al BFIC, consente di adattare la lunghezza delle linee di trasmissione e ricezione, mantenendo la spaziatura del reticolo di 15 mm. La Figura 6 mostra l'altro lato del PCB, che contiene i connettori RF a una distanza di 15 mm. In un sistema planare reale, questi connettori sarebbero sostituiti da antenne patch.

In questo layout di cella i condensatori di disaccoppiamento dell'alimentazione sono ridotti al minimo. La maggior parte del disaccoppiamento dell'alimentazione riguarda il BFIC. Anche i moduli TR hanno un disaccoppiamento di alimentazione sulla scheda, ma la maggior parte di questi condensatori non è tecnicamente necessaria, a causa del disaccoppiamento interno dell'alimentazione. I condensatori aggiuntivi sulla scheda sono stati una scelta progettuale conservativa e la spaziatura del reticolo di 15 mm ha fornito spazio sufficiente per questi condensatori.

Un altro obiettivo importante del layout della cella è stato quello di mantenere al minimo i transienti di commutazione sulle linee di polarizzazione, in modo da ridurre al minimo anche i tempi di switch. Questo obiettivo è stato raggiunto mantenendo la lunghezza di queste linee il più breve possibile per ridurre le componenti parassite della linea. Con le linee RF e il disaccoppiamento dell'alimentazione sul layer superiore, le linee di bias del PA e dell'LNA dal BFIC al modulo TR dovevano essere instradate sui layer interni 4 e 5 del PCB. Le varie linee di controllo digitale al BFIC dal microcontrollore sono state instradate sul layer 5, come mostrato nella Figura 7 e nella Figura 8. Su array più grandi, con tracce necessariamente più lunghe tra il controllore e i BFIC e/o velocità di clock più elevate, è necessario effettuare simulazioni di integrità del segnale per tenere conto di tutti i ritardi di propagazione delle tracce e garantire la corretta sincronizzazione del timing digitale.

Sulla scheda del sistema phased array planare di ADI, la traccia RFIO è breve e va immediatamente a un connettore; pertanto, il suo isolamento rispetto alle altre porte è elevato. Tuttavia, su una scheda applicativa planare phased array reale, è necessario prestare attenzione quando si effettua il routing delle porte dell'antenna del modulo TR e della porta RFIO, in particolare le porte dell'antenna del Canale 2 e dell'antenna del Canale 3 mostrate nella Figura 5, poiché si trovano sullo stesso lato del layout della cella della porta RFIO. In modalità di trasmissione, i percorsi hanno un guadagno maggiore rispetto alla modalità di ricezione; pertanto, il requisito di isolamento (separazione) tra i percorsi è maggiore, per evitare instabilità e oscillazioni.

Gestione termica

In un sistema phased array planare, con il gruppo di antenne su un lato della scheda e i componenti sull'altro, il dissipatore di calore deve essere posizionato sul lato componenti della scheda. Ciò rappresenta una sfida per la creazione di una soluzione di gestione termica che rimuova efficacemente una quantità sufficiente di calore dai vari componenti, in particolare dai PA, in modo che nessuno di essi superi la sua temperatura massima di giunzione.

Opzioni per la gestione del calore in un’antenna planare Phased Array

A causa della posizione dell'array di antenne sul lato posteriore della scheda, la soluzione di gestione termica non può consistere in uno schema in cui il calore viene convogliato dai paddle di massa di un componente, attraverso le vie termiche, verso un dissipatore di calore montato sul lato posteriore. Al contrario, il calore deve fluire direttamente dal lato superiore del componente o viaggiare indirettamente attraverso la base del componente stesso, nel PCB, muovendosi lateralmente prima di tornare a un dissipatore di calore sul lato componenti. Questo concetto è illustrato nella Figura 9.

Esistono due opzioni possibili per la conduzione del calore lontano dai componenti:

- Il dissipatore di calore entra in contatto con una ampia superficie del layer di massa superiore (lato componenti).

- Il dissipatore entra in contatto con il lato superiore dei componenti.

La progettazione del dissipatore di calore dipende in larga misura dai valori di dissipazione di potenza e di resistenza termica dei componenti. La maggior parte dei componenti ha una bassa resistenza termica tra la giunzione e l'involucro inferiore (θJC-BOTTOM) e una resistenza termica relativamente alta tra la giunzione e l'involucro superiore. Pertanto, lo schema mostrato nella Figura 9a è generalmente più efficace.

Si tratta di decidere se mettere a contatto anche il lato superiore dei componenti o meno. Se la resistenza termica tra giunzione e top (θJC-TOP) fosse dello stesso ordine di grandezza di θJC-BOTTOM (ad esempio, θJC-TOP < 5 × θJC-BOTTOM), il contatto del dissipatore con il lato superiore del package dei componenti fornirebbe un ulteriore percorso parallelo, utile per la conduzione del calore. Il metallo del dissipatore di calore non deve entrare direttamente in contatto con la parte superiore del package, in quanto ciò potrebbe causare sollecitazioni meccaniche. Al contrario, si dovrebbe usare un pezzo di nastro termoconduttivo o un pad di trasferimento termico, come mostrato nella Figura 9b.

Un esempio reale di dissipazione del calore sul lato del componente di un phased array planare è mostrato nella Figura 10. Si tratta della stessa scheda front-end con phased array planare mostrata nella Figura 1, solo con il dissipatore di calore applicato. All'interfaccia tra il dissipatore di calore e la massa metallica esposta sulla scheda (materiale bianco lungo il bordo del dissipatore di calore) è visibile un composto termoconduttivo. Si noti anche l'assenza di alette nelle aree strategiche, per consentire l'accesso alle porte di ingresso/uscita RF dei BFIC ADAR1000.

Progetto della cavità del dissipatore

La dissipazione del calore sul lato componenti costringe ogni cella di quattro moduli TR e un beamformer a trovarsi all'interno di una cavità metallica. Occorre prestare attenzione al dimensionamento e alla progettazione di questa cavità. Per garantire che la cavità non interagisca con i circuiti e non provochi instabilità o oscillazioni, è necessario eseguire una simulazione elettromagnetica.

L'analisi delle cavità metalliche, sia a scopo di schermatura che di gestione termica, non può essere trascurata alle alte frequenze. Generalmente le modalità risonanti sono supportate quando la dimensione maggiore della cavità è superiore o uguale a una mezza lunghezza d'onda (λ/2) della frequenza operativa nello spazio libero. L'energia irradiata dai circuiti e dalle tracce del PCB all'interno della cavità non ha modo di propagarsi al di là dei confini della cavità stessa, con conseguente instabilità e comportamento oscillatorio dei circuiti attivi.

Per attenuare gli effetti indesiderati delle risonanze di cavità si possono impiegare varie tecniche. Queste possono essere complesse, come strutture metalliche specifiche all'interno della cavità per supportare solo le risonanze a frequenze al di fuori dell'intervallo di funzionamento. Una tecnica molto più semplice è il posizionamento di un materiale assorbente RF all'interno della cavità, per attenuare l'energia dei modi risonanti. L'assorbitore è composto da materiali che creano un'alta permittività e un'alta permeabilità ai campi elettrici e magnetici, rispettivamente, per un intervallo di frequenze operative. È analogo ad un filtro elettrico taglia-banda.

Le dimensioni meccaniche delle cavità del dissipatore di calore della scheda del sistema phased array planare di ADI supportano risonanze a frequenze comprese nell'intervallo operativo. Per attenuare gli effetti delle modalità risonanti, all'interno di ogni cavità è stato installato un assorbitore RF, che smorza le risonanze senza compromettere le prestazioni della scheda. L'attenuazione dell'assorbitore RF varia da circa 20 dB/cm a 50 dB/cm nella banda di frequenza di funzionamento, abbassando di fatto il fattore Q del risonatore a cavità.

La simulazione elettromagnetica della cavità del dissipatore e dell'assorbitore RF è stata eseguita con lo strumento di simulazione EMPro simulation tool di Keysight. È stato costruito un modello semplice per analizzare una singola cavità, composto dal progetto meccanico della cavità del dissipatore di calore, dal materiale del PCB e da una massa di materiale per emulare gli IC fissati al PCB. Sono state eseguite due simulazioni, utilizzando il motore di simulazione con metodo a elementi finiti, per calcolare le risonanze autogene all'interno della cavità. Il materiale della cavità, per la prima simulazione, è stato definito come aria e ha dato luogo a risonanze autogene con un fattore Q elevato. Nella seconda simulazione, al posto dell'aria come materiale della cavità è stato utilizzato un assorbitore RF, che non ha prodotto autogeni. Il secondo caso di simulazione ha mostrato che il materiale dell'assorbitore selezionato ha abbassato il fattore Q della cavità, sopprimendo l'energia risonante all'interno della stessa. Per garantire l'accuratezza, i due casi di simulazione sono stati verificati con i dati misurati dell'hardware. Le frequenze in cui sono supportati i modi di risonanza e l'abbassamento del fattore Q da parte dell'assorbitore RF possono essere osservati nelle due misure di guadagno mostrate nella Figura 11. Queste misure prima e dopo confermano le previsioni della simulazione ed evidenziano l'importanza dell'analisi elettromagnetica.

Gestione dell’alimentazione

I phased array planari dotati di BFIC e moduli TR richiedono solitamente diversi domini di tensione di alimentazione. Per i circuiti di supporto del BFIC e del modulo TR possono essere necessari domini aggiuntivi, come un'alimentazione digitale a bassa tensione e/o una tensione step-down intermedia per alimentare i domini di alimentazione richiesti.

Per la progettazione dell'albero di alimentazione, di solito si sceglie una tensione comune, ad esempio 12 V, per alimentare tutti i blocchi di gestione energetica. È possibile generare in modo semplice ed efficiente le linee di tensione comuni di +5 V e +3,3 V, così come le linee di tensione negative comuni di -5 V e -3,3 V.

I PA e gli LNA che utilizzano FET depletion mode spesso richiedono che i loro gate siano polarizzati a una tensione negativa, prima di aumentare la tensione di drain, per evitare di danneggiare il dispositivo. Il corretto sequencing delle tensioni di drain e di gate risulta quindi cruciale e deve essere preso in considerazione durante la progettazione della soluzione di gestione dell'alimentazione.

Progetto dell’albero di gestione dell’alimentazione

La Figura 12 mostra l'albero di alimentazione utilizzato per fornire tensioni ai BFIC e ai moduli TR che si trovano sulla scheda phased array planare precedentemente menzionata. L'ingresso a 12 V pilota un circuito hot swap, dotato di controller ADM1172 hot swap, che fornisce una tensione protetta di 12 V con un limite di corrente di 8,33 mA al ramo dell'albero di alimentazione che alimenta gli IC ADAR1000 e ADTR1107.

Dai 12 V protetti, le alimentazioni a 3,3 V e 5 V che alimentano ADAR1000 e ADTR1107 sono generate da una coppia di regolatori sincroni step-down Silent Switcher, rispettivamente LT8642 e LT8652. Questi regolatori assicurano un basso livello di rumore e di spurie sulle alimentazioni RF critiche. L'LT8642 fornisce 3,3 V per l'alimentazione principale dell'ADAR1000 e la VDD per lo switch e l'LNA dell'ADTR1107, mentre l'LT8652 fornisce la VDD a 5 V per il PA dell'ADTR1107.

Per generare le tensioni di alimentazione negative necessarie all'ADAR1000 e all'ADTR1107, viene generata un'alimentazione negativa intermedia di -6 V dalla linea protetta a 12 V, utilizzando il regolatore invertente DC-DC ADP5074. A sua volta, l'ADP5074 pilota in parallelo due regolatori lineari negativi: LT3093 e LT3094, che generano rispettivamente i -3,3 V per lo switch VSS dell'ADTR1107 e i -5 V per l'ADAR1000.

Un ramo secondario dell'ingresso a 12 V alimenta il regolatore di commutazione step-down LT8606 e il regolatore lineare a bassissimo rumore ADP150, che forniscono rispettivamente un'alimentazione separata da 3,3 V e un'alimentazione digitale da 1,8 V.

Sequencing di accensione

L'accensione dell'albero illustrato nella Figura 12 è complessa. Richiede che l'utente immetta segnali di controllo specifici in momenti precisi durante l'intera sequenza di power-up. Il sequencing dei segnali di controllo critici è riportato nella Figura 13.

Per avviare la sequenza di accensione, occorre innanzitutto applicare l'alimentazione a 12 V alla scheda, dopodiché vengono alimentati i seguenti elementi:

- Le alimentazioni varie da 3,3 V e quelle digitali da 1,8 V dell'LT8606 e dell'ADP150 si attivano immediatamente.

- Una volta che l'ADM1172 hot swap fornisce il suo segnale di power good (HOT_SWAP_PG, segnale di controllo 1 nella Figura 13), l'ADP5074 si attiva e fornisce la sua linea negativa a -6 V.

L'accensione dell'LT8606, dell'ADP150 e dell'ADP5074 avviene automaticamente e non richiede alcun input da parte dell'utente.

In secondo luogo, i restanti regolatori si accendono in una sequenza specifica, in modo da non danneggiare il PA ADTR1107. La sequenza viene avviata mediante il fronte di salita di un segnale di accensione (POWER_UP_DOWN_IN, segnale di controllo 2 nella Figura 13) a un flip-flop D, che mantiene uno stato alto sulla sua uscita. L'uscita del flip-flop D viene messo in AND con il segnale di accensione dell'hot swap. Se entrambi i segnali sono alti, il segnale di abilitazione del sequencer (SEQ_EN) viene asserito alto sull'ADM1186-2. L'ADM1186-2 consente a ciascun regolatore LDO 47 ms per l'accensione (altrimenti viene generata una condizione di errore). Tra l'accensione di ciascun regolatore LDO vengono inseriti altri 2,2 ms di ritardo. L'esatta sequenza di abilitazione del regolatore LDO è la seguente:

- Il pin OUT1 dell'ADM1186-2 (segnale di controllo 3 nella Figura 13) si attiva e comanda il pin di enable del regolatore LDO a 3,3 V dell'LT8642; l'LT8642 dispone di 47 ms per asserire il suo segnale di power good al pin VIN1 dell'ADM1186-2; si verifica un ritardo di 2,2 ms.

- Il pin OUT2 dell'ADM1186-2 si asserisce alto e pilota il pin di abilitazione del regolatore LDO a -3,3 V dell'LT3093; l'LT3093 ha 47 ms per asserire il suo segnale di alimentazione al pin VIN2 dell'ADM1186-2; si verifica un ritardo di 2,2 ms.

- Il pin OUT3 dell'ADM1186-2 si asserisce alto e pilota il pin di abilitazione del regolatore LDO a -5 V dell'LT3094; l'LT3094 ha 47 ms per asserire il segnale di alimentazione al pin VIN3 dell'ADM1186-2; si verifica un ritardo di 2,2 ms.

- Il pin OUT4 dell'ADM1186-2 si attiva e comanda un gate AND il cui altro ingresso è un segnale di controllo a 5 V. Il pin PWDGD dell'ADM8611-2 si posiziona quindi su un valore alto.

A questo punto, l'ADAR1000 è completamente alimentato insieme allo switch ADTR1107 e all'LNA.

In terzo luogo, l'ADAR1000 viene programmato in modo che il bias del suo PA esca a -2 V (segnale di controllo 4 nella Figura 13), che è il valore di sicurezza per il PA dell'ADTR1107 durante l'accensione a +5 V. Una volta programmate tutte le uscite di polarizzazione del PA, il fronte di salita di un segnale di controllo a 5 V (segnale di controllo 5, 5 V_CTRL_IN, nella Figura 13) pilota un flip-flop D che mantiene uno stato alto sulla sua uscita. Il flip-flop pilota una porta AND il cui altro ingresso è il pin OUT4 dell'ADM1186-2. La porta AND attiva il pin di abilitazione del regolatore a 5 V dell'LT8652 e avvia l'ultima linea di alimentazione. La soluzione complessiva di power up sequencing è illustrata nella Figura 13.

Monitoraggio dell’alimentazione

L’LTC2992 monitora l'alimentazione erogata dai regolatori LT8642 e LT8652. Questa viene monitorata misurando la tensione attraverso un resistore di rilevamento, presente su ciascuna uscita del regolatore. La tensione viene campionata con un ADC on-chip e può essere letta tramite la porta I2C.

L'LTC2992 dispone anche di quattro pin GPIO, che possono essere utilizzati per rilevare lo stato dei segnali digitali. I quattro segnali digitali rilevati sono:

- il segnale power good dall’LT8652;

- il segnale enable del sequencer che pilota il pin UP/DOWN dell’ADM1186-2;

- il segnale power good del sequencer dall’ADM1186-2;

- il segnale di controllo 5 V (5 V_CTRL) che abilita il regolatore

Lo stato dei pin GPIO può essere letto anche attraverso la porta I2C. La soluzione per il monitoraggio dell'alimentazione è illustrata nella Figura 14.

Il monitoraggio dell'alimentazione e il rilevamento del segnale digitale forniti dall'LTC2992 contribuiscono a garantire il corretto funzionamento delle alimentazioni principali di ADAR1000 e ADTR1107. Il monitoraggio dell'alimentazione può anche fungere da strumento di debug e da built-in-test (BIT) per gli stessi chip ADAR1000 e ADTR1107. I singoli chip dell'array possono essere isolati e alimentati per verificare che consumino la corretta quantità di energia.

Il rilevamento GPIO dell'LTC2992 consente all'utente di sapere se l'LT8652 si è alimentato correttamente, monitorando il suo segnale power good. In questo modo, gli utenti possono assicurarsi che il segnale di controllo a 5 V sia basso finché non sono pronti per l'accensione a 5 V dei PA ADTR1107. Il rilevamento GPIO fornisce anche lo stato di sequencing dell'ADM1186-2, ossia rileva se i regolatori LDO si stanno accendendo o spegnendo e se la sequenza di accensione/spegnimento è completa.

Conclusione

In questo articolo abbiamo analizzato le sfide associate alla progettazione del front-end RF di un sistema phased array planare. I vincoli dimensionali, che derivano dalla spaziatura del reticolo richiesta alle alte frequenze, richiedono approcci innovativi alla progettazione dei circuiti. Queste sfide possono essere ridotte in modo significativo grazie all'uso di BFIC e moduli TR, che si interfacciano facilmente tra loro. Questa interfaccia "glueless" ha il vantaggio di consentire tracce RF più corte e meno linee di controllo, con il risultato di ottenere sistemi con risposte rapide e più facili da calibrare. I semplici controlli a singolo pin e la memoria on-chip del BFIC consentono transizioni e avanzamenti rapidi del beam. Poiché un lato del PCB è riservato all'array di antenne patch, per implementare un dissipatore di calore efficace è necessario scendere a compromessi. L'analisi e la progettazione della cavità del dissipatore sono fondamentali per evitare le oscillazioni. Una soluzione di gestione dell'alimentazione con un corretto sequencing del front end RF è cruciale per il progetto complessivo del sistema, al fine di mantenere al minimo il rumore, le frequenze spurie ed evitare danni agli amplificatori.

I circuiti descritti in questo articolo provengono dalla scheda di prototipazione analogica beamforming per banda X/ku ADAR1000EVAL1Z, che può essere acquistata presso Analog Devices.