Ogni chip che esce da una linea di produzione trascorre parte del proprio tempo su apparecchiature automatizzate di test, dove la sua memoria, le interfacce di I/O, la circuiteria analogica e digitale vengono accuratamente esaminate. Tipicamente responsabile del 10-50% del tempo totale di collaudo, il test della logica digitale può rappresentare una parte significativa del costo complessivo del prodotto. Benché costoso, il test è un passaggio critico del processo globale di sviluppo di un chip. I dati indicano che gli investimenti del settore in termini di Ate (Automated test equipment) ammontano a circa 4 miliardi di dollari all'anno. Man mano che i progetti dei chip crescono in termini di dimensioni e complessità, in particolare ai nodi più avanzati, i costi dei test aumentano di conseguenza. Nel corso degli anni abbiamo visto la comunità che si occupa di Design for Test proporre diverse tecnologie orientate alla riduzione dei costi, ma negli ultimi tre o quattro lustri non si è affermato nulla di natura veramente rivoluzionaria. Oggi, la compressione di test Xor-based - che offre rapporti tipici da 50 a 100X - rimane la più utilizzata. La compressione Xor riduce il tempo di test suddividendo i registri di un progetto in un numero di catene superiore al numero dei pin di scansione presenti sul chip per la connessione all’Ate. A 16/14nm, tuttavia, i progettisti SoC stanno manifestando l'esigenza di spingere la compressione dei vettori di scansione al di là di 100X al fine di controllare il costo di test ed evitare di investire nuove risorse nell'acquisto di tester supplementari. Chiaramente, il mercato è maturo per una nuova metodologia che contribuisca a minimizzare ulteriormente i costi di test.

Limitazioni della compressione Xor tradizionale

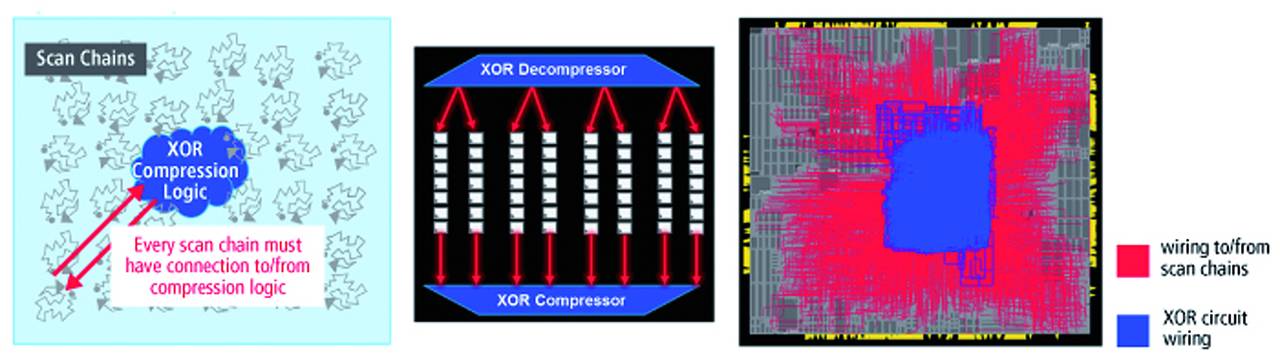

In un'architettura di compressione Xor tradizionale, quando il rapporto tra il numero di catene di scansione e il numero di pin di scansione aumenta, la lunghezza di ciascuna catena di scansione diminuisce, riducendo di conseguenza il numero di cicli di clock necessari per fare avanzare il pattern di test. A parità di pattern, la riduzione del numero di cicli di clock implica la riduzione del tempo totale di test sull’Ate, con un conseguente risparmio in termini di costi di collaudo. Meno cicli di clock per pattern significa anche disporre di meno bit in ciascun pattern per controllare i valori di registro e rilevare i guasti. In questo scenario, un rapporto di compressione più elevato diventa problematico. Se il rapporto di compressione diventa troppo alto, la copertura nei confronti dei guasti scende, soprattutto in presenza di anomalie che richiedono il controllo di un numero di valori di registro superiore rispetto ai bit disponibili nel pattern di test. Anche se la copertura di guasto può essere mantenuta, quando il rapporto di compressione aumenta il numero di pattern necessari cresce rapidamente poiché diventa più difficile inserire il rilevamento di guasti multipli in un singolo pattern. In definitiva, aumentare il rapporto di compressione comporta un beneficio ridotto sul tempo totale di test. Un rapporto di compressione più alto ha inoltre una ripercussione sostanziale sulla configurazione fisica di un chip: ogni catena di scansione deve infatti essere collegata alla logica di compressione Xor. Con un rapporto di compressione tipico di 100X, l'impatto medio sul totale delle risorse di interconnessione del circuito integrato di un codec Xor per una gamma di componenti digitali comuni è nel range del 3-5%. Quali sarebbero gli effetti aumentando il rapporto di compressione a 400X, in particolare per soddisfare le esigenze di test dei progetti ai nodi avanzati? Ebbene, l'impatto sulle risorse di routing del chip aumenterebbe al 10%. Ciò costringerebbe ad aumentare le dimensioni del die, vanificando eventuali risparmi sui costi derivanti dalla riduzione del tempo di test.

Aumentare il rapporto di compressione

Ora, cosa succederebbe se si potesse aumentare il rapporto di compressione a 400X, senza alcun impatto sulla copertura dei guasti o sulle risorse di routing del chip? Ciò è quanto si ripromette la nuova tecnologia di test Cadence, denominata Modus Test Solution. Sviluppata sulla base di un'architettura a compressione elastica 2D in attesa di brevetto, la nuova soluzione Cadence consente di raggiungere rapporti di compressione superiori a 400X riducendo fino a un terzo del tempo di test digitale rispetto alla compressione Xor tradizionale.

La compressione elastica 2D combina una compressione 2D e una compressione elastica. La compressione 2D sfrutta la natura bidimensionale del dispositivo, distribuendo la logica di compressione e decompressione intorno al perimetro del die. La griglia 2D instrada gli stimoli e i dati di risposta da/verso i canali di scansione, riducendo al minimo le interconnessioni necessarie per effettuare i collegamenti necessari al codec. A parità di dimensioni di die, la ridotta congestione della compressione 2D permette di raggiungere rapporti di 400X con la stessa lunghezza dei percorsi utilizzati nella compressione 100X basata sulla metodologia tradizionale. La struttura a griglia ottenuta grazie alla compressione 2D permette di ridurre fino a 2,6 volte le risorse di routing necessarie rispetto ai circuiti di compressione Xor unidimensionali tradizionali con un rapporto di compressione 100X. La compressione elastica integra il decompressore con degli elementi sequenziali. Ciò consente di aggiungere in modo efficace dei bit al cubo di scansione, senza allungare le catene. Durante la generazione automatica del pattern di test (Atpg), è possibile gestire i bit di controllo sequenzialmente su più cicli di scansione: tale funzionalità consente di mantenere la copertura dei guasti su livelli elevati, soprattutto in presenza di anomalie difficili da rilevare che richiedono un gran numero di bit di controllo. Per supportare ulteriormente la rilevazione dei guasti più difficili, il decompressore elastico può aumentare adattativamente il numero di cicli di trasferimento in un pattern di test superando la lunghezza della catena di scansione. Per garantire l’efficacia del test di memoria nei moderni processori ad alta velocità, Modus Test Solution prevede il supporto per un bus condiviso, comune per Cpu ad alte prestazioni. Integrato perfettamente con le funzionalità Pmbist (Programmable memory Bist) esistenti, il supporto del bus di test condiviso offre un'unica interfaccia alla periferia della Cpu che permette l'accesso alle memorie interne. Ciò consente di applicare la tecnica Bist in modo efficace senza impattare i percorsi di temporizzazione critici nella Cpu ad alte prestazioni e nei chip di networking. Tale funzionalità include anche algoritmi di test programmabili per Sram FinFet e per applicazioni di sicurezza automotive.