Un innovativo approccio, sviluppato congiuntamente da Siemens e da PDF Solutions, migliora il processo di ottimizzazione della resa sui nodi di processo avanzati, individuando alcuni dei fattori che limitano la resa nel corso della fase di produzione in serie su elevati volumi.

Il miglioramento delle rese rappresenta l’elemento chiave per realizzare una riduzione dei costi di produzione e dunque una massimizzazione dei profitti, in un mercato estremamente competitivo come quello dei semiconduttori. Se, da un lato, i fattori responsabili delle più importanti limitazioni della resa vengono sempre affrontati nelle fasi iniziali del processo, mediante un’apposita attività di yield ramping, è anche vero che ad essa comunque sfuggono alcuni pattern sistematicamente presenti nel layout, i quali continuano a provocare, in modo più sottile, la comparsa di difetti fisici nel corso della fase di produzione in grande serie.

I team di Ricerca e Sviluppo del gruppo Tessent di Siemens, unitamente a quelli di PDF Solutions, hanno sviluppato un nuovo approccio che combina l'analisi dei pattern, realizzata mediante lo strumento FIRE di PDF Solutions, con una diagnosi di scansione logica su ampia scala, effettuata utilizzando la tecnologia RCD (Root Cause Deconvolution) di Siemens EDA. Il motore di analisi dei pattern FIRE provvede ad individuare numerosi gruppi di pattern del layout tra loro simili (denominati famiglie di pattern) aventi caratteristiche potenzialmente sospette, dopodiché il software di machine learning basato sulla diagnosi RCD di Tessent produce dei diagrammi di Pareto relativi a tutti i potenziali difetti e al loro impatto sulla resa. Questi diagrammi di Pareto delle rese, nei quali tutte le specifiche famiglie di pattern del layout vengono considerate come distinte cause prime della difettosità totale, evidenziano la possibilità di aumentare l'accuratezza complessiva dell’analisi dal 70% circa al 90% circa. Gli autori di Siemens EDA e di PDF Solutions hanno descritto questi risultati in un documento presentato alla conferenza IEEE SPIE Advanced Lithography + Pattern del 2023; l’approccio utilizzato viene sinteticamente riassunto nel presente articolo.

Come risolvere il problema dei difetti sistematici

Una possibile classificazione dei difetti di produzione consiste nel suddividerli tra casuali oppure sistematici, laddove i difetti di tipo sistematico indicano che la prevalenza dei guasti è associata alla presenza di determinate caratteristiche riconoscibili, come ad esempio specifiche caratteristiche geometriche dell'intorno locale al punto del difetto. Esistono tecniche che consentono di contrastare tali effetti legati all’ambiente circostante, ma ciononostante alcuni difetti sistematici del tutto nuovi, oppure inaspettati, possono ancora fornire il principale contributo a sensibili cali delle rese, persino in una fase ormai matura delle moderne tecnologie.

Il prossimo passo che è possibile compiere per migliorare la resa consiste quindi nell’identificare quegli ulteriori difetti di tipo sistematico. Si tratta di identificare i diversi pattern legati ad anomalie e di quantificarne l’impatto. Tuttavia, i metodi tradizionali disponibili – basati su tecniche di imaging mediante microscopio elettronico a scansione, o SEM (Scanning Electron Microscope), seguite da un’analisi puntuale dei guasti fisici - richiedono tempo e denaro, nonché la conoscenza a priori di informazioni sulle posizioni dei difetti. Non possono quindi essere applicati ad un numero sufficientemente elevato di campioni, tale da permettere di quantificare l'impatto sulla resa globale del prodotto. Serve un metodo in grado sia di quantificare l'impatto dei diversi pattern, che di fornire le posizioni di tali pattern.

Ecco come è stato affrontato questo problema:

- Analizzando la geometria del prodotto, per individuare tutte le posizioni in cui può verificarsi un difetto e rilevando i pattern presenti nell’intorno di queste posizioni.

- Raggruppando i pattern in famiglie, come illustrato in Figura 1.

Utilizzo di strumenti potenti: software diagnostico per la scansione logica

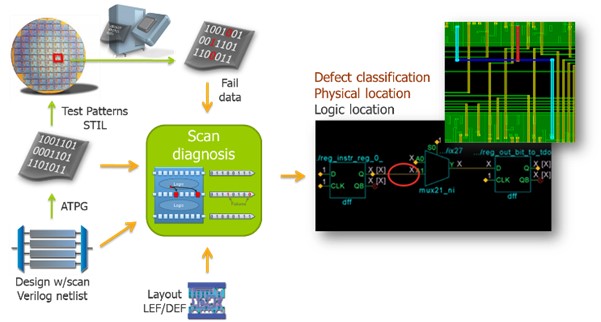

Nel campo dei progetti digitali, lo standard de-facto per il testing di produzione è costituito dai pattern di scansione generati mediante uno strumento automatico di ATPG (Automatic Test Pattern Generation). Questi pattern di scansione contengono sia i segnali di stimolo da applicare che le relative risposte valide, calcolate mediante una simulazione del progetto logico. Il prodotto fisico ottenuto dal progetto viene quindi testato applicandovi i modelli di scansione generati dall'ATPG del progetto stesso, mediante l’utilizzo di un’apposita apparecchiatura di test automatizzata, o ATE (Automatic Test Equipment), la quale provvede anche ad acquisire tutte le risposte non conformi alle attese. Questi dati relativi ai test falliti (i pattern di scansione, unitamente alle due viste, logica e fisica, del progetto) vengono poi utilizzati da un software specializzato nella diagnosi della scansione, al fine di produrre un report dettagliato, secondo il processo illustrato in Figura 2.

Il tipico report diagnostico della scansione, prodotto da uno strumento che sfrutta la conoscenza del layout e delle celle, fornisce informazioni relative alle posizioni ed alle proprietà fisiche tali da consentire di comprendere il motivo dei difetti rilevati. Questi report guidano le successive analisi della difettosità e della resa. Può inoltre rivelarsi particolarmente efficace una diagnosi su larga scala, che è costituita da un esteso set di diagnosi di scansione, che mira a convertire i dati sui test falliti in un elenco delle posizioni fisiche sospette presenti in ogni die difettoso. Per una analisi della resa di questo tipo si possono utilizzare efficaci tecniche di machine learning, come la deconvoluzione delle cause prime, o RCD (Root-Cause Deconvolution), che aiutano a formulare un’interpretazione dei risultati contenuti in una collezione molto estesa di report diagnostici di scansione.

Come inserire nell'analisi RCD le informazioni sulle famiglie dei pattern

La normale tecnica di RCD è stata appositamente arricchita, specializzandola in modo da farle apprendere le problematiche di calo sistematico della resa dovute a caratteristiche funzionali del layout, fornendole i dati delle diverse famiglie di pattern ricavati dall'analisi del layout del progetto. Le informazioni sulle famiglie di pattern contengono un elenco dei singoli punti potenzialmente difettosi rilevati nel layout fisico, con la loro posizione (x, y e layer). Ad ogni punto viene inoltre associata la famiglia di pattern cui appartiene, nonché la possibilità che esso rappresenti un circuito aperto oppure un cortocircuito.

La Figura 3 mostra il flusso corrispondente all’importazione di queste informazioni nel setup dello strumento di diagnosi su larga scala. Nel primo step le posizioni dei punti vengono abbinate alle reti logiche presenti nella netlist dei gate. Questo è uno step di setup da svolgere una tantum, finalizzato a fornire al database diagnostico dei layout di Tessent una mappa di ogni segmento della rete, collegando la sua posizione nel progetto all’elenco dei potenziali punti difettosi presenti nel segmento stesso.

Nel corso dell’attività di diagnosi queste informazioni di mappatura vengono quindi utilizzate per annotare ogni punto sospetto identificato dall’algoritmo diagnostico con le informazioni relative alla relativa famiglia di pattern del layout. Infine, quando i risultati della diagnosi su larga scala vengono elaborati utilizzando la RCD, l’informazione relativa alla famiglia di pattern del layout viene aggiunta all'elenco delle potenziali cause alla radice del difetto. Questo elenco è quello da cui la RCD acquisisce i valori necessari per elaborare il diagramma di Pareto dei difetti, per quella determinata popolazione di die difettosi.

Il risultato della RCD con l’utilizzo delle famiglie di pattern del layout

Si consideri il fatto che all’interno di un moderno progetto possono essere presenti centinaia di migliaia di differenti famiglie di pattern del layout. Derivare un diagramma di Pareto dei difetti che abbraccia un numero così elevato di possibili cause purtroppo aumenta significativamente la possibilità di convergere su una conclusione sbagliata. Per ovviare a questo problema, la RCD provvede a filtrare in modo intelligente le soluzioni altamente improbabili, escludendo le famiglie di pattern del layout appartenenti alla "coda" del diagramma, che difficilmente possono essere le principali responsabili del calo della resa.

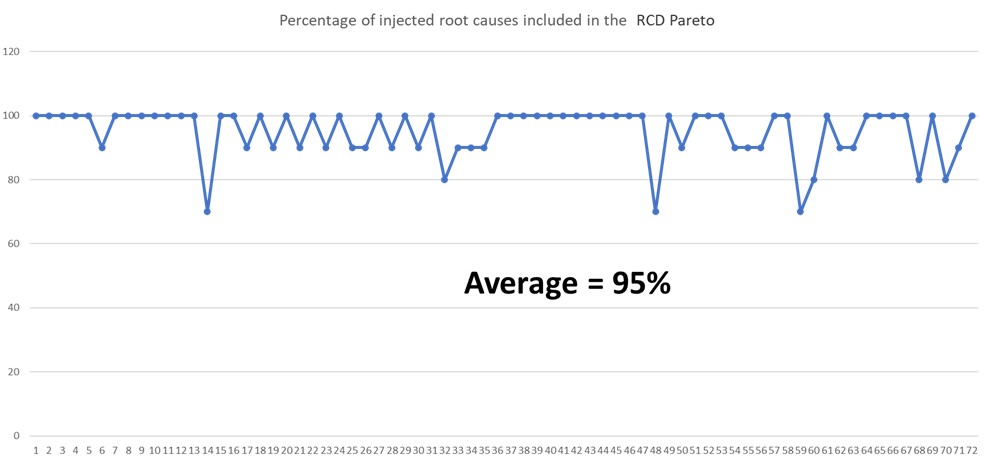

Si è provveduto a testare questa metodologia all’interno di un ambiente simulato, nel quale sono state create più popolazioni distinte di die volutamente contenenti dei difetti, generati sulla base di altrettanti diagrammi di Pareto della difettosità. Per ogni diagramma di Pareto sono stati infatti create alcune centinaia di die difettosi, iniettando i difetti nella simulazione, per poi sottoporre a diagnosi i log dei difetti risultanti dai test. Infine, i risultati della diagnosi su larga scala sono stati inseriti nel motore di machine learning RCD arricchito nel modo precedentemente descritto. Il diagramma di Pareto così ottenuto è stato quindi confrontato con il diagramma di Pareto iniziale, quello utilizzato per creare la simulazione, al fine di misurare l'accuratezza raggiunta nell'identificazione delle diverse famiglie di pattern del layout iniettate nei die.

Questo esperimento è stato ripetuto con settantadue diverse popolazioni, ognuna avente un proprio diagramma di Pareto, con l’intento di misurare l'accuratezza media ottenuta con diversi scenari di difetti. I risultati sono documentati nella Figura 4. Il grafico mostra che la percentuale media di cause prime iniettate nella simulazione e correttamente riconosciute è pari al 95%.

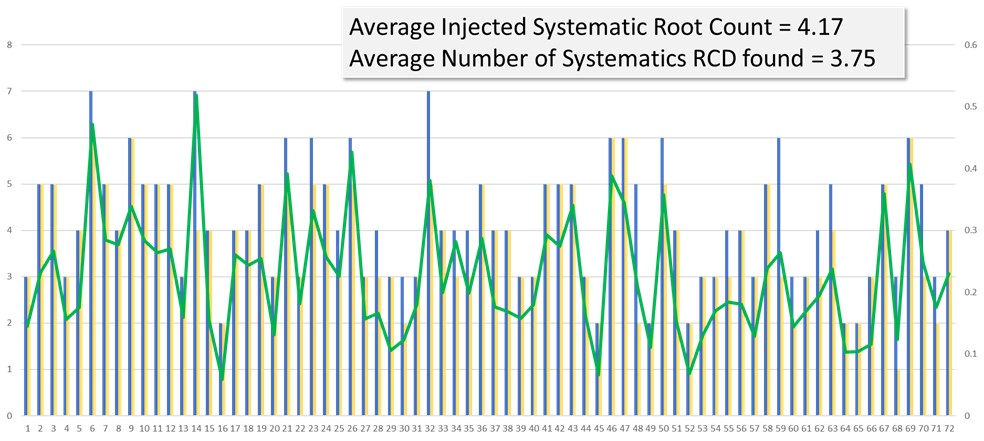

La Figura 5 mostra che, per quanto riguarda specificamente le cause prime associate a famiglie di pattern del layout ripetute in modo sistematico, sono state correttamente riconosciute, in media, 3,75 delle 4,17 cause prime sistematiche iniettate nel progetto. Questi dati dimostrano i vantaggi offerti da questa metodologia nella identificazione, a partire dai dati dei test di produzione, di difettosità sistematiche presenti nel progetto e precedentemente sconosciute.

In sintesi

Il raggiungimento e il mantenimento di elevate rese, nella produzione di semiconduttori basati sulle odierne tecnologie di processo più avanzate, è un’attività che continua a rappresentare una sfida impegnativa per il settore. Il nuovo metodo appena illustrato aiuta ad individuare tipologie di difetti che, introdotti in modo sottile dall’interazione tra il progetto e particolari pattern del layout presenti in modo sistematico, possono provocare significativi cali delle rese. La combinazione di una efficace analisi dei pattern del layout (mediante FIRE), della diagnostica mediante scansione logica e della RCD promette di poter portare alla luce tali problemi senza la necessità di condurre una minuziosa analisi dei singoli guasti. Utilizzando i pattern del layout e i dati relativi ai test logici falliti, i risultati della simulazione sopra descritta indicano che si può riporre elevata fiducia (attendibilità pari al 95%) sul fatto che questa metodologia fornirà un concreto aiuto anche nei reali contesti di produzione dei progetti. Siemens EDA continuerà a collaborare sia con partner che con clienti per convalidare la metodologia su set di dati molto estesi, provenienti da layout e da diagnosi di reali scenari di produzione. Per ulteriori informazioni su questo approccio per una diagnosi su larga scala, è possibile consultare il sito web di Siemens.