Dopo avere rilasciato lo scorso anno sul mercato una serie di prodotti innovativi in tecnologia da 28 nm, come i SoC interamente programmabili, e gli IC 3D interamente programmabili, Xilinx propone in questo 2013 un'altra significativa innovazione, lanciando il primo dispositivo da 20 nm e il primo dispositivo interamente programmabile da 20 nm nell'industria dei semiconduttori. Dispositivo basato sulla prima architettura programmabile di classe Asic disponibile sul mercato, chiamata UltraScale. “Con il programma di rilascio di dispositivi a 20 nanometri più aggressivo sul mercato, ritengo che Xilinx sia un anno avanti rispetto al concorrente più prossimo nei dispositivi di alta fascia e circa sei mesi avanti per i dispositivi di fascia intermedia,” ha affermato Giles Peckham, Marketing Director di Xilinx in occasione del lancio internazionale avvenuto a inizio estate.

La collaborazione

con Tsmc

Xilinx ha lavorato con Tsmc per infondere i requisiti degli Fpga di fascia alta all'interno del processo di sviluppo SoC Tsmc 20, proprio come ha fatto nello sviluppo del processo 28 HPL. La collaborazione sulla tecnologia da 28 nm ha prodotto il primo rilascio di un dispositivo da 28 nm sul mercato e dei primi dispositivi Fpga, SoC e IC 3D interamente

programmabili, ponendo Xilinx una generazione avanti in termini di rapporto prezzo/prestazioni/watt, di integrazione di sistemi programmabili e di riduzione del costo della distinta materiali. Xilinx ha ora esteso questa formula collaudata per dominare il mercato dai 28

nm fino ai 20 nm, rendendo disponibile sul mercato la prima architettura programmabile di classe Asic, denominata UltraScale.

“Quando combinate la tecnologia di Tsmc, la nostra architettura UltraScale, e la co-ottimizzazione con la nostra suite di progettazione Vivado, crediamo di essere circa un anno avanti nel fornire prestazioni a livello di sistema ed un livello di integrazione superiore di un fattore 1,5 - 2 - l'equivalente di una generazione avanti rispetto alla concorrenza.” ha sottolineato Peckham.

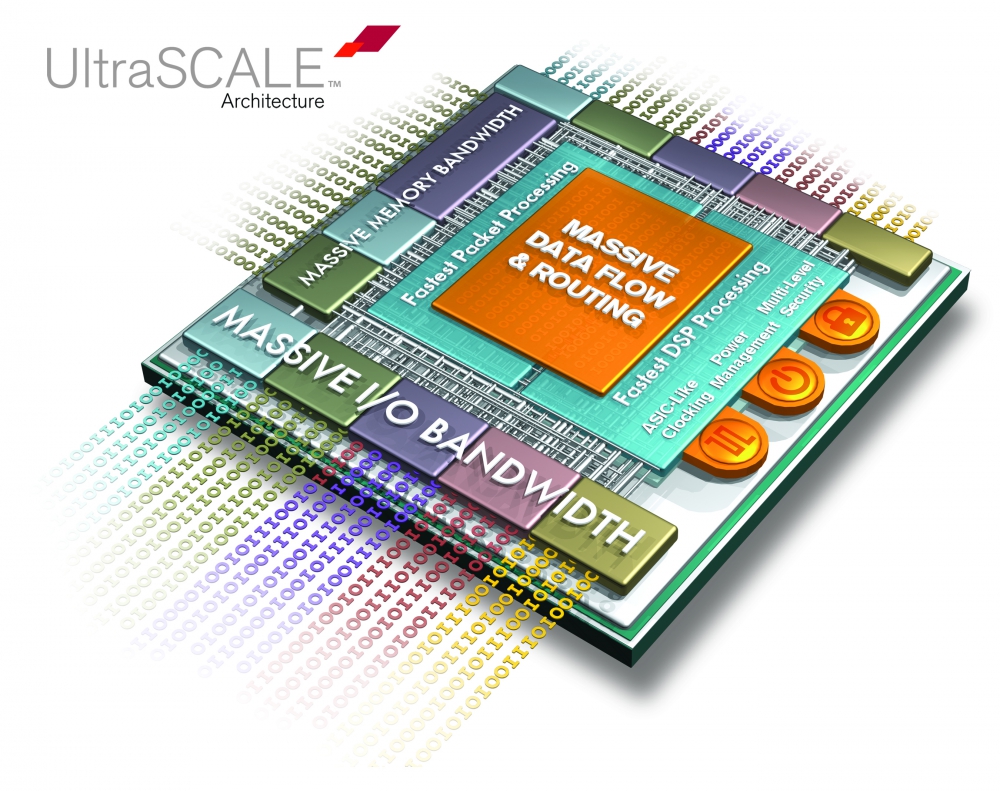

L'architettura

UltraScale

L'architettura UltraScale è stata sviluppata per scalare dalla tecnologia planare da 20 nm ai 16 nm e al di là delle architetture FinFet, e dai dispositivi monolitici fino agli IC 3D. Non solo ovvia alle limitazioni di scalabilità della capacità di trasmissione e della latenza totale del sistema, ma aggredisce direttamente il collo di bottiglia numero uno delle prestazioni dei chip in corrispondenza dei nodi avanzati: le interconnessioni. È richiesto un approccio architetturale innovativo per gestire i livelli di prestazioni a livello di sistema da più Gigabit al secondo con l'elaborazione intelligente alla piena velocità di linea scalando dai terabit ai teraflop. L'esigenza non è semplicemente di aumentare le prestazioni di ciascun transistor o blocco del sistema, o di scalare il numero dei blocchi nel sistema, ma fondamentalmente di migliorare la comunicazione, la distribuzione del clock, i percorsi critici e

le interconnessioni per supportare il massiccio flusso di dati e l'elaborazione in tempo reale dei pacchetti, dei segnali digitali e delle immagini. L'architettura UltraScale risponde a tutte queste

sfide applicando le tecniche Asic di punta in un'architettura completamente programmabile:

• un flusso dati massiccio ottimizzato per bus ampi che supportano una capacità di trasmissione da più terabit;

• distribuzione multi-regione, gestione dell'alimentazione e sicurezza di prossima generazione di tipo Asic;

• percorsi critici altamente ottimizzati e memoria ad alta velocità incorporata, in cascata per rimuovere i colli di bottiglia nei Dsp e nell'elaborazione dei pacchetti;

• funzione a gradino in banda inter-die per l'integrazione dei sistemi IC 3D di seconda generazione;

• abbondanti risorse in termini di I/O e di banda di memoria con una riduzione drastica della latenza e un'interfaccia ottimizzata per la memoria ampia dell'IC 3D;

• eliminazione della congestione nell'instradamento dei segnali e co-ottimizzazione con i tool Vivado per un'utilizzazione del dispositivo superiore al 90% senza degrado nelle prestazioni.

Per sistemi sempre

più intelligenti

I primi dispositivi UltraScale andranno a estendere le famiglie di Fpga Virtex e Kintex e dei circuiti integrati 3D, ora basate sulla tecnologia di processo da 28 nm, e serviranno anche come base per i futuri SoC interamente programmabili Zynq. Essi consentiranno la realizzazione della prossima generazione di sistemi intelligenti, caratterizzati da requisiti architetturali ad alte prestazioni:

• Otn 400G con elaborazione intelligente dei pacchetti e gestione del traffico;

• Lte in modalità Mista 4X4 con Radio Wcdma con beamforming intelligente;

• display 4K2K e 8K con riconoscimento e miglioramento intelligente delle immagini;

• sistemi ad alte prestazioni per sorveglianza e riconoscimento intelligente;

• applicazioni di calcolo ad alte prestazioni per i data center.

Oltre le logiche programmabili

Moshe Gavrielov, Ceo di Xilinx ha aggiunto: “Con il primo rilascio sul mercato di dispositivi in tecnologia da 20 nm, della prima architettura UltraScale di classe Asic, della prima Design Suite Vivado di classe SoC, della proprietà intellettuale in continua espansione, e delle soluzioni C, Arm e basate su processore per sistemi più intelligenti, Xilinx sta ancora una volta espandendo il valore aggiunto e la penetrazione di mercato dell'industria Pld. Stiamo inoltre fornendo un'ulteriore generazione di valore aggiunto ai nostri clienti un anno in avanti rispetto alla concorrenza.”