RISC-V è un’architettura di set di istruzioni (ISA – instruction set architecture) open-source diventata uno standard de facto per l’implementazione di qualunque unità di calcolo integrata e specializzata all’interno di un sistema elettronico. La natura open-source dell’architettura RISC-V e la sua flessibilità d’uso in diversi progetti elettronici stanno generando un vero e proprio terremoto in un mercato dei semiconduttori storicamente dominato da modelli di business proprietari, come quello di Arm. Osservata in prospettiva, la tecnologia RISC-V minaccia potenzialmente, non nell’immediato, anche il comparto commerciale rappresentato dalla famiglia di architetture x86, tradizionalmente detenuto da Intel e AMD, per le CPU (centralprocessing unit) dedicate al mondo dei computer, dei server e dei data center.

La particolarmente favorevole fase evolutiva che questo standard sta attraversando, sia dal punto di vista della maturazione tecnologica dello standard e dell’ecosistema di aziende che lo sostengono, sia sotto il profilo commerciale, appare visibilmente testimoniata dalla mole di attività e collaborazioni in atto nel settore, nonché dagli ultimi risultati finanziari. Una fase di sviluppo dunque particolarmente positiva e ricca di fermento, messa in luce a più riprese anche durante il RISC-V Summit North America 2025, organizzato in ottobre a Santa Clara, California, da RISC-V International. L’evento ha presentato un programma in agenda fitto di keynote, appuntamenti, demo, sessioni verticali, case study, aggiornamenti e approfondimenti sull’avanzamento delle attività nei diversi gruppi di lavoro che partecipano al progetto.

Cos’è RISC-V e quanto è importante

L’acronimo RISC (reduced instruction set computer) fa riferimento a computer con un’architettura di set di istruzioni semplificata, rispetto all’architettura CISC (complex instruction set computer), mentre la lettera “V” rappresenta la quinta generazione di architetture del set di istruzioni RISC, la cui origine viene fatta risalire, tra la fine degli anni ’70 e l’inizio degli anni ’80, all’epoca della coniazione del termine da parte di David Patterson, professore all’Università della California - Berkeley. Disponendo di un set di istruzioni ridotto, i computer RISC eseguono un numero limitato e semplice di istruzioni per compiere un dato task. La filosofia RISC non è dunque un concetto nuovo, ma con la definizione e l’avvio del progetto RISC-V, nel 2010, si dà vita a un’architettura di set di istruzioni open-source e royalty-free, poi pubblicata sotto licenza BSD (Berkeley Software Distribution). Nel 2015 viene istituita la RISC-V Foundation, oggi nota come RISC-V International, per mantenere e pubblicare la proprietà intellettuale relativa alla ISA di base e tutte le sue estensioni. Nel 2016 comincia la transizione di RISC-V, da tecnologia emergente, a standard industriale, commercialmente diffuso ai livelli oggi raggiunti.

Nel 2024 Renesas annuncia l’introduzione di quelli che definisce i primi microcontrollori (MCU) a 32 bit general-purpose basati su RISC-V del settore, costruiti con un core CPU sviluppato internamente. Le MCU RISC-V R9A02G021 sono indirizzate a diversi mercati finali, che includono sensori IoT, elettronica di consumo, dispositivi medicali, piccoli elettrodomestici e sistemi industriali.

A marzo 2025, Infineon, con l’obiettivo di aprire la strada all’adozione di RISC-V nel settore automotive, rende noto il lancio di una nuova famiglia di microcontrollori basati su RISC-V e dedicati all’industria automobilistica. La nuova famiglia di MCU entrerà a far parte della linea di prodotti AURIX, consolidato marchio di microcontrollori per il settore automobilistico sviluppati da Infineon.

A ottobre 2025, la società taiwanese Upbeat Technology, pioniera nelle soluzioni ultra-low power di elaborazione dati, voce, e rilevamento edge AI, e SiFive, fornitrice di soluzioni IP e silicio per processori RISC-V commerciali, introducono sul mercato la famiglia di MCU UP201/UP301, una serie di microcontrollori RISC-V dual-core di nuova generazione progettati per offrire un’efficienza energetica estremamente elevata. Demo delle nuove MCU sono state presentate anche in occasione del RISC-V Summit di Santa Clara. La famiglia di MCU UP201/UP301 stabilisce un nuovo punto di riferimento nell’edge computing, dichiara Upbeat Technology, almeno per due ragioni: da un lato integra due core IP SiFive Essential e due acceleratori AI progettati da Upbeat, raggiungendo prestazioni per watt di primo piano nel settore. Dall’altro e consente l’implementazione di dispositivi IoT, wearable device, droni e inferenza edge AI in modalità always-on.

Le ragioni del decollo commerciale

Essendo open-source, l’architettura RISC-V non richiede il pagamento di royalty o commissioni di licenza per la sua implementazione. Un vantaggio non da poco, specialmente per startup, aziende con budget limitati, ma anche per qualunque organizzazione voglia ridurre i costi di produzione. RISC-V, diversamente dalle ISA proprietarie, rende accessibile a un’ampia platea di organizzazioni la progettazione dei processori, senza la necessità di sottostare ai vincoli contrattuali dei grandi licenziatari.

Inoltre, pur avendo un set di istruzioni base molto snello, RISC-V è stato sviluppato con una struttura modulare che consente l’aggiunta di estensioni standard o istruzioni personalizzate (custom extensions). Tale flessibilità permette di realizzare processori altamente specializzati e ottimizzati per casi d’uso specifici, che spaziano dall’implementazione di capacità di calcolo per la edge AI, alle MCU per l’industria automobilistica, alle applicazioni IoT (Internet of Things), ai data center. L’opportunità di evitare lo sviluppo di funzionalità non necessarie permette di semplificare il design del dispositivo, portando a miglioramenti della velocità di esecuzione, a una riduzione del consumo energetico e a una minor dissipazione di potenza.

L’attuale successo di RISC-V rispetto alle architetture RISC che lo hanno preceduto può spiegarsi, da un lato, con il fatto che lo standard ha raggiunto uno stato di stabilità sufficiente a convincere i grandi investitori a mobilitare con fiducia risorse economiche. Su un altro versante, considerando gli enormi volumi di chip IoT prodotti annualmente, le architetture proprietarie (Arm), basate su un modello di licenza che richiede il pagamento di royalty, generano costi che tendono a diventare sempre più insostenibili per i produttori.

Vanno poi messi in conto il trend crescente delle soluzioni di accelerazione dell’intelligenza artificiale, e la domanda di calcolo ultra specializzato. Le aziende sono alla ricerca di acceleratori hardware estremamente specializzati e ottimizzati. Diversamente dalle architetture proprietarie, che limitano la capacità di personalizzare l'ISA, RISC-V, come accennato, in virtù delle custom extension aiuta i progettisti a realizzare chip su misura (domain-specific), che ottimizzano i requisiti PPA (power, performance, area) in confronto ai core generici.

Non da ultimo, va analizzato il fattore geopolitico, che porta le organizzazioni a concentrare sempre più l’attenzione sul valore della sovranità tecnologica. Essere dipendenti da tecnologie proprietarie come le architetture Arm o x86, rispettivamente detenute da Regno Unito/Giappone e Stati Uniti d’America, rappresenta una preoccupazione strategica globale, per i rischi potenziali derivanti da restrizioni o sanzioni commerciali eventualmente imposte da tali paesi.

The SHD Group: “Mercato RISC-V oltre le aspettative”

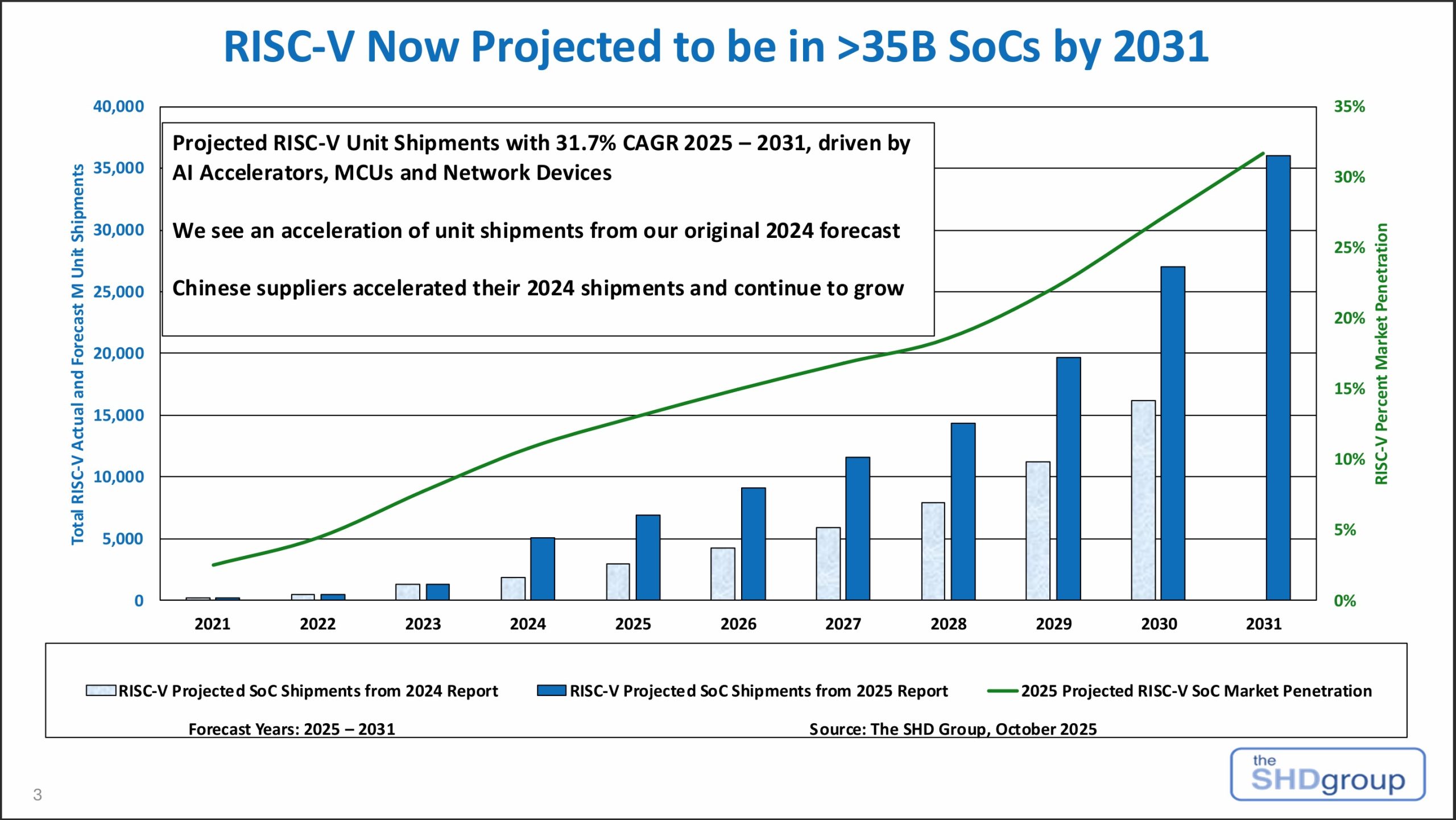

Stando alle ultime stime presentate al RISC-V Summit dalla società di ricerche di mercato The SHD Group, quest’anno l’architettura RISC-V è andata davvero oltre sestessa. Rispetto alle previsioni sulle spedizioni di SoC (system-on-chip) RISC-V calcolate nel rapporto 2024 stilato dagli analisti, le previsioni su tali spedizioni che compaiono nel rapporto 2025 mostrano performance molto migliori. In altre parole, la tecnologia RISC-V sta crescendo oltre le aspettative, ha spiegato Richard Wawrzyniak, principal analyst, per ASIC, SoC e IP, in The SHD Group. Al punto che ora la società prevede spedizioni per oltre 35 miliardi di unità SoC RISC-V entro il 2031, e un trend di crescita che registrerà un CAGR (tasso annuo di crescita composto) pari al 31,7% (2025 – 2031), guidato da acceleratori AI, MCU (microcontroller unit) e dispositivi di rete. La ragione di questa accelerazione nelle spedizioni di unità rispetto alla previsione originaria del 2024, chiarisce Wawrzyniak, è che i fornitori cinesi nel 2024 hanno aumentato le loro consegne, e continuano a crescere.

Dove sta la forza di uno standard aperto

Al di là delle performance cinesi, il perché la tecnologia RISC-V stia crescendo oltre ogni aspettativa, secondo Wawrzyniak, si spiega considerando alcuni aspetti tecnologici ed elementi strategici particolarmente importanti. In primo luogo, l’architettura RISC-V e il suo ecosistema in crescita hanno reintrodotto la ‘concorrenza’ nel panorama della progettazione dei SoC, in quanto le estensioni personalizzate (custom) di RISC-V favoriscono l’innovazione e garantiscono prestazioni su misura. Inoltre, il divario di prestazioni tra i core CPU Arm e RISC-V di fascia alta si sta riducendo, con una parità quasi totale prevista entro la fine del 2026.

Secondariamente, l’adozione di SoC basati su RISC-V è favorita dalla diffusione di un numero sempre maggiore di applicazioni di intelligenza artificiale. Quest’ultima, ricorda, è presente su PC, smartphone e altri dispositivi mobili, oltre che su una serie di dispositivi edge AI. Inoltre, con l’aumentare delle prestazioni e la diminuzione dei costi della AI, nuove applicazioni per l’intelligenza artificiale continueranno a emergere. La flessibilità di personalizzazione di RISC-V è una soluzione particolarmente adatta per l’accelerazione dell’AI.

In terzo luogo, la natura eterogenea dei SoC ha creato opportunità per molteplici architetture CPU, in quanto i system-on-chip sono in grado di supportare sia RISC-V, sia altre ISA, consentendo agli ingegneri di scegliere per le varie applicazioni il core più adatto per ogni funzione.

Infine, i fornitori di IP (intellectual property) per CPU RISC-V continuano a introdurre nuovi e più potenti core CPU, aumentando le prestazioni e le funzionalità, ed estendendo la portata dell’IP delle CPU RISC-V ad applicazioni che richiedono una maggiore potenza di calcolo.

Attori consolidati e nuovi entranti

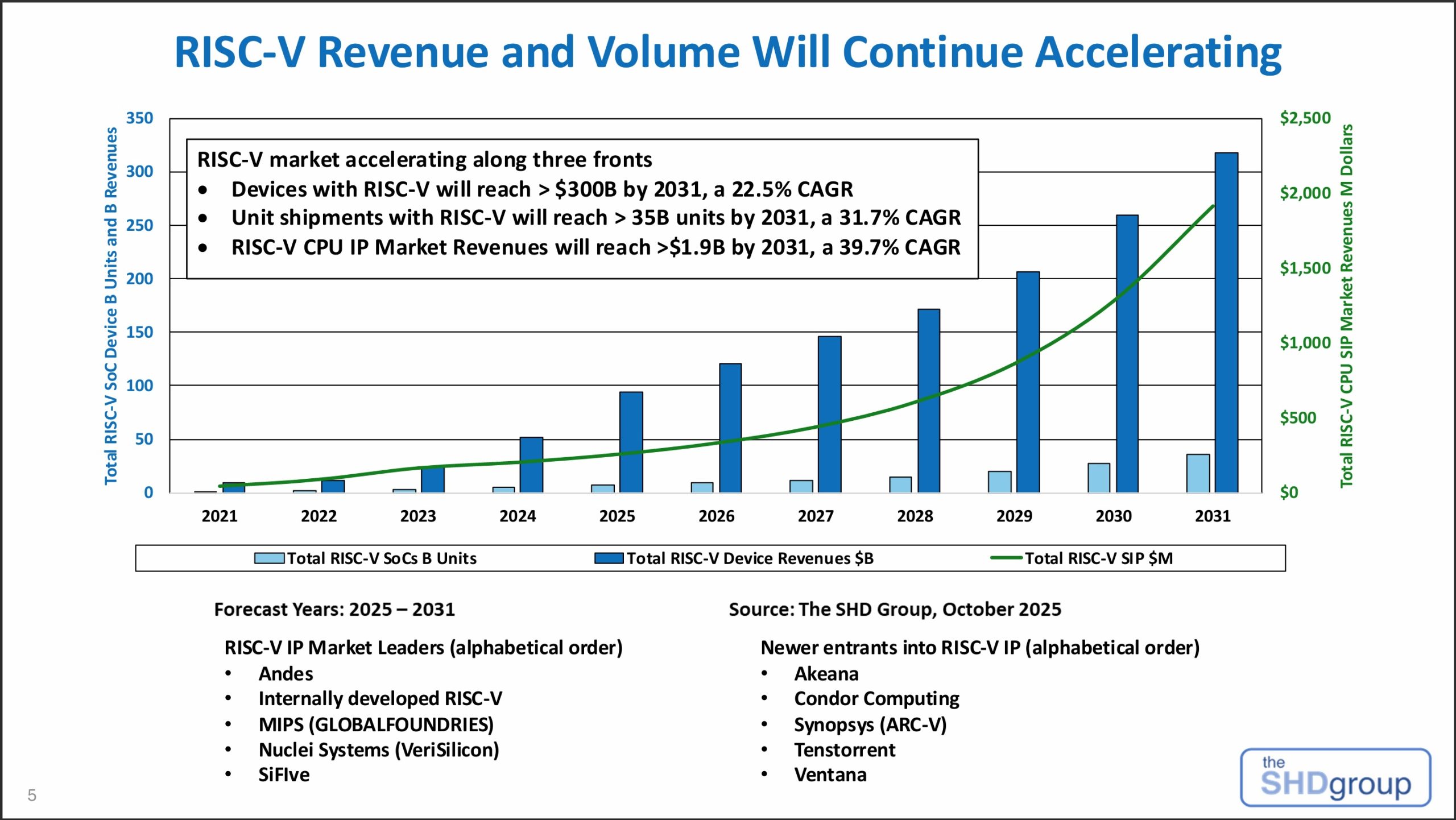

In particolare, aggiunge Wawrzyniak, il mercato RISC-V accelera su tre fronti contemporaneamente. Uno è il versante dei dispositivi con RISC-V, che raggiungeranno un valore di oltre 300 miliardi di dollari entro il 2031, registrando un CAGR del 22,5%. Vi sono poi, come accennato, le spedizioni di unità con RISC-V, che raggiungeranno 35 miliardi di unità (CAGR 31,7%), e ci sono i ricavi derivanti dal mercato dell’IP per le CPU RISC-V, che toccheranno 1,9 miliardi di dollari, sempre entro il 2031 (CAGR 39,7%).

Oltre ai principali protagonisti del comparto, tra cui figurano Andes Technology Corporation, MIPS – acquisita in agosto da GlobalFoundries -, Nuclei System(VeriSilicon), SiFive, e altri attori che sviluppano RISC-V internamente, il rapporto di The SHD Group indica nuovi operatori entranti nel settore dell’IP per RISC-V, come Akeana, Condor Computing (filiale R&D di Andes Technology), Synopsys (IP ARC-V), Tenstorrent, Ventana.

In termini di penetrazione totale del mercato, RISC-V raggiungerà oltre il 33% entro il 2031, mentre i settori con la penetrazione più elevata risultano quello automobilistico e dei prodotti di consumo. Il rapporto individua anche diverse esigenze di accelerazione dell’intelligenza artificiale che stanno alla base del trend di crescita di RISC-V. Dal sondaggio emerge il desiderio delle organizzazioni di disporre di un’unica tecnologia in grado di accelerare tutte le reti neurali attualmente presenti sul mercato. Tuttavia, la rapida evoluzione della tecnologia AI e l’introduzione continua di nuove reti neurali impediscono che ciò avvenga. Le esigenze di personalizzazione costituiscono poi un altro fattore trainante del mercato per l’IP e il silicio RISC-V.

Progressiva affermazione

RISC-V è già diventata la seconda architettura più diffusa dopo Arm, conclude il rapporto di The SHD Group, indicando alcuni trend significativi. Infatti, nonostante i volumi iniziali di tecnologia RISC-V siano stati trainati da applicazioni ‘deeply embedded’, come storage, dispositivi indossabili, reti, sensori intelligenti e quant’altro, attualmente è in corso la transizione verso applicazioni di fascia più alta, che includono, ad esempio, l’adozione di RISC-V nelle infrastrutture di data center, nei sistemi ADAS (advanced driver assistance system), e nel computing, via via che l’intelligenza artificiale si espande verso tali applicazioni.

C’è poi l’annuncio da parte di Nvidia, lo scorso luglio al RISC-V Summit 2025 in Cina, dell’utilizzo di RISC-V in tutti i propri componenti, ricorda la società di ricerche: ciò in sostanza conferma l’importanza di RISC-V e potrebbe eliminare le obiezioni riguardo la sua adozione. Per inciso, Nvidia ha annunciato che la sua piattaforma software CUDA (Compute Unified Device Architecture) sarà resa compatibile, lato CPU, con l’architettura del set di istruzioni RISC-V. Si tratta dunque di un passo importante, per consentire l’utilizzo delle CPU basate su RISC-V in applicazioni che richiedono prestazioni elevate, perché RISC-V può ora fungere da processore principale per i sistemi basati su CUDA, svolgendo un ruolo tradizionalmente ricoperto dai core x86 o Arm. Il porting di CUDA su RISC-V indica un ulteriore potenziale di espansione. Inoltre,anche la collaborazione di recente annunciata tra Nvidia e Intel potrebbe aumentare le possibilità di un’ulteriore penetrazione di RISC-V nel mercato. In quest’ultimo l’utilità di RISC-V, aggiunge il rapporto, continua ad essere confermata dal fatto che questa ISA open-source viene adottata da altri attori del comparto, come Broadcom, Google, Meta, ma anche MediaTek, Qualcomm, Renesas, Samsung. Ancora, l’ascesa dell’intelligenza artificiale e delle architetture ISA eterogenee nei SoC fungono da acceleratori per l’adozione di questo standard. Le implementazioni personalizzate aiutano poi i progettisti a dimensionare correttamente i core delle CPU.