La crescente domanda di super-chip e acceleratori AI rende i chiplet una soluzione alternativa sempre più emergente, per superare le limitazioni insite nei system-on-chip (SoC) monolitici.

I chiplet tornano in auge, tra sfide e opportunità tecnologiche, con la promessa di rivoluzionare il futuro dei semiconduttori, e trasformare il design e la fabbricazione dei chip. Quello di chiplet non è propriamente un concetto nuovo, ma questo paradigma architetturale di progettazione di circuiti integrati sta ultimamente acquisendo popolarità, e registrando sul mercato una fase di accelerazione. Ripresa spiegabile con la confluenza di diversi fattori, sia tecnologici, sia economici e, soprattutto, con la crescente richiesta di super-chip e acceleratori AI, guidata dal boom dell’intelligenza artificiale. La letterale esplosione sul mercato delle applicazioni AI, e in particolar modo di quelle che integrano la AI generativa (GenAI), ha creato una domanda senza precedenti per chip ad altissime prestazioni, gli AI accelerator, appunto.

Ecosistema tecnologico in espansione

Sul mercato si possono oggi ritrovare vari esempi di applicazione dei chiplet, sia nei prodotti di elettronica di consumo, sia in quelli per il mondo aziendale. I processori delle linee Ryzen ed EPYC di AMD sono basati su architettura Zen, che utilizza chiplet. Anche Intel, nella quarta generazione di processori Xeon Scalable (nome in codice Sapphire Rapids) ha adottato un’architettura che sfrutta un approccio multi-tile (multi-chip) e la soluzione d’interconnessione 2.5D chiamata EMIB (Embedded Multi-die Interconnect Bridge).

L’industria dei chiplet non è priva di una ricca fioritura di startup: la californiana Persimmons fornisce sistemi di inferenza GenAI (generative AI) flessibili, a basso consumo energetico, basati sulla piattaforma chiplet proprietaria PL1000. Enosemi, acquisita a maggio 2025 da AMD, sviluppa chiplet elettronici e fotonici ad alta velocità. In marzo, invece, Axelera AI, fornitrice di tecnologia di accelerazione hardware AI appositamente progettata per la AI generativa e l’inferenza della visione artificiale all’edge, ha annunciato Titania, un chiplet di inferenza AI ad alte prestazioni, in grado di fornire scalabilità ed elevata efficienza energetica.

Piattaforma chiplet per la AI fisica

Il trend di intenso fermento tecnologico è confermato, tra le varie attività del comparto, anche da un recente annuncio, lo scorso novembre, da parte di Cadence, dell’avvio con successo della fase di bring-up del silicio per il suo ‘system chiplet’, che costituisce un componente core della propria piattaforma chiplet per la physical AI. Il settore dei semiconduttori, spiega la società, sta avanzando a un ritmo senza precedenti, spinto dalla necessità di prestazioni più elevate, maggiore integrazione e massima efficienza. Con il rallentamento della legge di Moore, sottolinea, approcci innovativi come le architetture basate su chiplet hanno assunto un ruolo centrale, in particolare per i progetti di AI fisica.

Il positivo completamento del bring-up, secondo Cadence, segna un nuovo standard per la progettazione di semiconduttori modulari e ad alte prestazioni, portando almeno tre benefici. In primo luogo, il fatto di aver dimostrato un system chiplet pienamente operativo, integrato con la memoria e altre interfacce critiche, dà ai futuri team di prodotto la fiducia necessaria per adottare tale piattaforma nella progettazione di potenti sistemi di AI fisica, consentendo al prodotto di passare, dalla fase concettuale, a quella di commercializzazione. Secondariamente, la validazione dell’approccio system chiplet all’interno di una piattaforma completa accelera la crescita di un ecosistema in cui gli ingegneri possono combinare in maniera affidabile i progetti di chiplet. In terzo luogo, questo progresso tecnologico, aggiunge Cadence, permette ora ai progetti di nuova generazione nelle aree dei sistemi ADAS (advanced driver assistance system) per il settore automobilistico, dei droni, della robotica, del mondo aerospaziale e della difesa, di beneficiare della flessibilità e della scalabilità prima limitate ai complessi e costosi SoC (system-on-chip) monolitici.

Chiplet: cosa sono, e che flessibilità offrono

L’approccio basato su chiplet è strettamente connesso ai principi cha da sempre governano il progresso tecnologico dei semiconduttori, un mondo in cui da decenni l’evoluzione dei circuiti integrati è stata guidata dallo sviluppo di chip via via più miniaturizzati, e caratterizzati da crescenti prestazioni ed efficienza energetica. Oggi però, più l’incessante processo di miniaturizzazione fa avvicinare l’industria elettronica ai limiti della legge di Moore, più il paradigma architetturale rappresentato dai chiplet emerge tra gli addetti ai lavori come la strada futura da intraprendere.

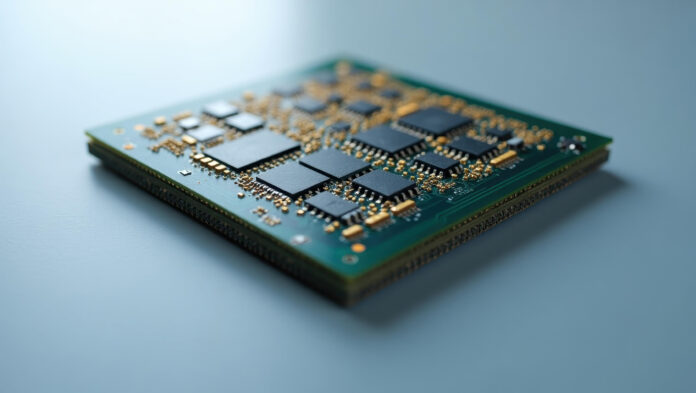

In elettronica, un chiplet si può definire come un minuscolo pezzo di silicio specializzato, progettato per svolgere una funzione specifica, e operare come parte di un sistema di chiplet. Ciò viene realizzato adottando un approccio “Lego-like”, in cui ciascun chiplet può essere combinato con altri chiplet all’interno dello stesso package, per formare un SiP (system-in-package), un ‘sistema in package’ complesso che, a seconda dei casi può essere, ad esempio, costituito da una CPU, una GPU (graphics processing unit) o un acceleratore AI. Questi sistemi di chiplet sono spesso chiamati utilizzando il termine ‘multi-chip module’ (MCM) per indicare un package che contiene molteplici die specializzati e separati, interconnessi su un singolo substrato.

L’adozione di tecniche avanzate di packaging dei semiconduttori, come il packaging 2.5D e lo stacking 3D con bonding ibrido, consentono di connettere i chiplet tramite collegamenti ad elevata larghezza di banda e bassa latenza. In aggiunta, ciascun chiplet può essere realizzato utilizzando il ‘nodo tecnologico’, o processo produttivo, più adatto per la funzione che deve eseguire: è quindi possibile, ad esempio utilizzare un processo produttivo più economico a 14 nm (nanometri), o 28 nm, per fabbricare chiplet di memoria, e un processo produttivo più avanzato e costoso, come quello a 3 nm, per realizzare chiplet di elaborazione ad alte prestazioni. Questa tecnica di integrazione eterogenea, che permette di combinare tra loro chiplet fabbricati con processi produttivi differenti, conferisce agli ingegneri la flessibilità di design richiesta per comporre di volta in volta un sistema il più possibile bilanciato, e ottimizzare, in ogni singolo progetto, i requisiti di costo, prestazioni, efficienza energetica. Tale flessibilità non si può raggiungere adottando la tradizionale filosofia architetturale basata su system-on-chip (SoC) monolitico, in cui i componenti del sistema finale, quindi CPU, memoria, controller, interfaccie di I/O, vengono integrati tutti insieme fin dall’inizio in un unico grande die.

Un paradigma alternativo all’approccio SoC

I progetti basati su chiplet, come accennato, rappresentano la risposta all’attuale rallentamento della legge di Moore, perché offrono un approccio alternativo per aumentare la densità di transistor, le prestazioni e l’efficienza economica del sistema, rispetto al paradigma SoC. Quest’ultimo si basa sulla miniaturizzazione del singolo die monolitico contenente tutti i componenti, che però è diventata troppo costosa e tecnologicamente complessa, soprattutto con l’avvento dell’intelligenza artificiale e la diffusione degli acceleratori AI.

Per supportare l’addestramento e il funzionamento di modelli AI di grandi dimensioni servono infatti super-chip, ossia processori con miliardi di transistor, e fabbricare chip monolitici così grandi, come le moderne GPU di fascia alta o gli acceleratori AI, diventa economicamente proibitivo, essenzialmente a causa del drastico calo della resa produttiva (yield) che si verifica all’aumentare delle dimensioni del die, ossia il singolo chip, la singola ‘fetta di silicio’ ricavata dal wafer. Più aumentano le sue dimensioni e il numero di transistor, più aumenta la probabilità di trovare difetti sulla superficie del die. I difetti di fabbricazione, causati da contaminanti, particelle di polvere, problemi di fotolitografia, o le imperfezioni prodotte da altri fattori, sono distribuiti in maniera casuale sulla superficie del wafer di silicio. Quindi, maggiore è l’area del die, maggiore è la probabilità che contenga almeno un difetto che lo renda non funzionante. La resa del die cala inoltre in maniera esponenziale in rapporto all’aumento delle sue dimensioni, quindi alla grandezza dell’area del chip. Considerando che con l’adozione dei nodi tecnologici più avanzati, come i processi produttivi a 3 nm, i costi di produzione dei wafer di silicio salgono enormemente, se la resa per singolo die cala esponenzialmente, ogni die difettoso rappresenta una perdita diretta significativa su questo costo di base già molto elevato.

Necessità del mercato e cammino di standardizzazione

Il perché i chiplet abbiano vissuto nell’ultimo anno un periodo di particolare importanza e notorietà lo si è visto e sperimentato anche al recente Chiplet Summit 2025, svoltosi a Santa Clara, California, che ha sostanzialmente confermato e accelerato l’agenda del settore verso un futuro completamente modulare. L’evento ha registrato iscrizioni e numero totale di partecipanti quasi raddoppiati rispetto al 2024, con aree chiave di interesse che hanno incluso i metodi di packaging avanzati, le interfacce die-to-die ad alta velocità, le applicazioni dell’intelligenza artificiale generativa e la ‘open chiplet economy‘. All’evento hanno contribuito con i propri keynote varie società, tra cui Cadence, Synopsys, Alphawave Semi, Arm, Teradyne, Keysight Technologies, e anche community come Open Compute Project (OCP).

Tra le tendenze del Summit, il dominio della AI e delle applicazioni che richiedono capacità di calcolo ad alte prestazioni (high performance computing – HPC) sono emersi come i fattori determinanti per portare l’adozione dei chiplet a diventare, non più una scelta, ma una necessità per questo genere di workload. In tema di accelerazione della AI, i chiplet sono considerati come la chiave per espandere la connettività e la potenza di calcolo richieste dai grandi modelli linguistici (large language model - LLM) e dalla AI generativa. Notevole enfasi viene posta sull’architettura SiP (system-in-package), in qualità di metodo a basso costo per supportare l’infrastruttura di calcolo massivo, soprattutto attraverso l’adozione di memoria HBM (high bandwidth memory) integrata tramite chiplet. Data la crescente potenza richiesta dagli acceleratori AI, l’attenzione si concentra inoltre sulle soluzioni di gestione termica, con discussioni sull'implementazione di sistemi di raffreddamento a liquido (liquid cooling) per gestire l’alta densità di potenza esistente nei package multi-chiplet.

L'industria sta inoltre concentrandosi sull’ottimizzazione del ciclo di vita del design per i sistemi multi-die. In altre parole, servono strumenti e workflow che consentano ai progettisti di analizzare l'integrità del segnale, e tool di analisi multifisica per studiare fin dalle prime fasi di progettazione i gradienti termici che possono causare condizioni di stress, sia a livello di singolo chiplet, sia di sistema completo. Ma sono richieste anche soluzioni di testing efficienti per il collaudo di sistemi SiP complessi basati su chiplet, per garantire che tutti i componenti assemblati funzionino correttamente.

Sfide di interoperabilità

Sul versante delle sfide di standardizzazione e interoperabilità dei chiplet, la maturazione degli standard aperti è considerata la base per lo sviluppo di un ecosistema di chiplet funzionale e competitivo. In questo ambito, l’adozione del protocollo di interconnessione Universal Chiplet Interconnect Express (UCIe) è stata ampiamente discussa, anche nella prospettiva di evoluzione verso la specifica UCIe 2.0, pubblicata ad agosto 2024, che introduce miglioramenti per l'integrazione 3D, le prestazioni e il packaging avanzato. Tra l’altro, ad agosto 2025, l’UCIe Consortium ha già annunciato l’introduzione della specifica 3.0 di UCIe (UCIe 3.0), che aggiunge ulteriori migliorie, e aumenta la velocità d’interconnessione tra chiplet, con il supporto per data rate a 48 GT/s (gigatransfers per second) e 64 GT/s, raddoppiando la banda fornita da UCIe 2.0 (32 GT/s). Tuttavia, UCIe 2.0 è ancora una tecnologia emergente, e la rapida pubblicazione della specifica UCIe 3.0 naturalmente non significa che la versione precedente sia obsoleta, ma riflette il livello di accelerazione tecnologica in atto nel settore. Un’accelerazione che richiede pianificazione a lungo termine, in particolare per affrontare i requisiti futuri dell'AI e dell'HPC, e consentire ai team di design di programmare la progettazione degli acceleratori AI che verranno prodotti dal 2028 in poi.

Industria dei chiplet: crescita del 24,8% fino al 2030

La crescente domanda di soluzioni elaborazione ad alte prestazioni ed efficienza energetica negli ambiti dell’intelligenza artificiale, delle applicazioni per data center e della tecnologia 5G guiderà l’espansione dell’industria dei chiplet: lo prevede un recente studio pubblicato da MarketsandMarkets, secondo cui, dai 51,94 miliardi di dollari del 2025, il mercato dei chiplet raggiungerà 157,23 miliardi di dollari entro il 2030, registrando un tasso annuo di crescita composto (CAGR) pari al 24,8%, nel periodo della previsione (2025-2030). L’ascesa di standard aperti come UCIe sta aprendo nuove strade per l’interoperabilità e la collaborazione tra i fornitori di semiconduttori. Inoltre, il crescente utilizzo dei chiplet nell’elettronica di consumo, nell’automotive e nell’edge computing amplia la base di applicazioni nel mercato. I continui progressi nelle tecnologie di packaging e interconnessione 2.5D/3D creano ulteriori opportunità di innovazione e di progettazione di chip economicamente vantaggiosi. In particolare, il packaging 3D, aggiunge lo studio, è una tecnologia che sta ridefinendo il panorama dei chiplet, perché consentendo di impilarli verticalmente, promette livelli senza precedenti di prestazioni, larghezza di banda e miniaturizzazione.

Tra i trend chiave del comparto, viene segnalato il segmento dei coprocessori ASIC (application specific integrated circuit) per i carichi di lavoro di intelligenza artificiale, che si stima registrerà la crescita più rapida durante il periodo di previsione, in ragione del design specializzato, ottimizzato per workload AI e di apprendimento automatico, e studiato per fornire prestazioni ed efficienza energetica superiori rispetto ai processori generici.