I complessi progetti di circuiti integrati sono oggi caratterizzati da un'ampia ricchezza funzionale e da un elevato numero di caratteristiche. Su un unico chip vengono comunemente ospitati molteplici processori, canali di I/O, diversi tipi di memorie, complessi circuiti analogici e di sintesi logica. È inoltre spesso necessario realizzare domini di alimentazione multipli, al fine di ridurre i consumi e migliorare l'efficienza dei progetti. Tra le attività volte ad accertare se l'IC progettato si comporterà esattamente come desiderato, quella della verifica svolge un ruolo importante. La verifica è normalmente basata sia sulla simulazione (per la compliance funzionale), sia su estensivi controlli di verifica fisica, per garantire che l'IC sia stato implementato correttamente. Vengono comunemente effettuati test di tipo Drc (Design Rule Checking), Erc (Electrical Rule Checking), confronti Lvs (Layout vs. Schematic), analisi Dfm (Design For Manufacturing), oltre a numerosi altri. Ciononostante, un numero crescente di report evidenzia la presenza di una classe di insidiosi errori di progetto particolarmente difficili da controllare mediante i metodi tradizionali, e potenzialmente rivolti ad un'ampia varietà di progetti IC, in particolar modo quelli in cui è indispensabile un'elevata affidabilità, come ad esempio le applicazioni per il settore delle comunicazioni, per il settore medico, o per quello automotive. I progettisti IC stanno imparando a identificare e correggere tali problemi di affidabilità prima del tape-out.

Gli approcci tradizionali

Tra gli approcci tradizionali utilizzati per affrontare le problematiche di affidabilità, quello più datato si affida al colpo d'occhio del progettista, il quale osservando il layout dell'IC tenta di individuare le strutture più esposte a potenziali problemi, per poter se necessario tornare sui propri passi ed operare ritocchi mirati nel layout. Naturalmente, questo approccio non è molto scientifico, né tantomeno ripetibile in modo schematico. Un approccio tradizionale di tipo più analitico si basa invece sulla simulazione che, tuttavia, oltre a richiedere lunghi tempi di esecuzione, produce dei risultati la cui qualità è direttamente legata alla bontà della netlist Spice estratta, dei modelli Spice, dei modelli di stress, e degli stimoli di input. Infine, un altro approccio convenzionale è costituito dall'utilizzo di tradizionali regole Drc per l'individuazione delle condizioni di affidabilità, il che comporta l'inserimento nel database del layout IC di layer aggiuntivi, o "marker layers". Il processo di aggiunta dei layer di marcatura è però manuale (dunque esposto ad alti tassi di errore) e richiede ulteriori passaggi Drc, dunque un ulteriore costo in termini di tempo.

Nuove regole per l'affidabilità

Per cercare di contrastare più efficacemente questo tipo di problemi, negli ultimi anni sono stati apportati significativi miglioramenti alle regole di affidabilità. La verifica di affidabilità consiste in una metodica per verificare la robustezza di un progetto sia a livello schematico che a livello del layout, a fronte di svariate regole di progettazione elettrica che formalizzano gli standard di performance degli IC. Il mancato rispetto di tali regole può tradursi in una riduzione della resa, in difetti non identificati che giungono fino ai clienti, ed in errori inaspettati che emergono sul campo — ogniqualvolta vi sono delle violazioni delle regole di affidabilità, la robustezza del progetto è compromessa. Per contro, un robusto controllo dell'affidabilità riduce la quantità dei die che manifestano malfunzionamenti elettrici irreparabili durante il collaudo finale, oppure malfunzionamenti prematuri durante la vita sul campo. Tra i team di progetto particolarmente attenti alle tecniche Erc avanzate, vi sono quelli impegnati nello sviluppo di apparecchiature submicron, mixed-signal, o low-power per l'impiego in campo mobile e altre applicazioni. Molte delle funzionalità Erc presenti nei migliori tool Drc ed Lvs di oggi riescono però a coprire solo un numero limitato di problematiche Erc. L'individuazione è assicurata solo se il problema ricade in una delle poche categorie predefinite. Purtroppo, i dati mostrano che il numero di controlli Erc e di affidabilità non coperti da queste casistiche predefinite è in crescita. E i requisiti necessari per l'implementazione di tali controlli sono spesso significativi, ed oltretutto specifici per ogni produttore o fonderia. Come si può immaginare, ciò rende alquanto difficile l'integrazione di un ampio numero di controlli all'interno dei vari strumenti Drc o Lvs. Le regole di affidabilità sono piuttosto complesse, non standardizzate, e in continua crescita sia in quantità che in tipologia. L'Erc convenzionale è basato sulle netlist, e non è in grado di identificare le classi più recenti di requisiti, che includono controlli relativi a dispositivi, reti o pin “floating”, alla rilevazione di gate troppo sottili connessi a voltaggi eccessivi, alle violazioni del massimo numero consentito di pass gate in serie, o alla ricerca di problemi legati all'uso di level shifter nei progetti. Alcuni controlli di affidabilità devono essere effettuati utilizzando sia la netlist che le informazioni sulla geometria del layout, come ad esempio la minima distanza “calda” NWELL tra due well. Inoltre, accade frequentemente che le regole di affidabilità siano specifiche dei singoli progetti, o siano sviluppate sulla base di conoscenze acquisite da progetti precedenti, oppure in previsione di potenziali difetti già attesi, il che crea la necessità di avere strumenti estremamente flessibili e configurabili dall'utente, per supportare lo sviluppo rapido e accurato di regole personalizzate.

Le sfide dell'affidabilità

Nei progetti odierni caratterizzati da molteplici domini di tensione e circuiti misti analogici/digitali, quali quelli per le apparecchiature low-power rivolte ai dispositivi mobili e ad altre applicazioni alimentate a batteria, le regole di affidabilità sono di importanza cruciale, ed al contempo particolarmente sfidanti. I progetti che incorporano controlli su molteplici domini di alimentazione sono particolarmente soggetti a errori di progettazione sottili e difficili da identificare nello spazio della simulazione o mediante l'utilizzo di tecniche PV tradizionali. Spesso, tali errori insidiosi non si manifestano sotto forma di un immediato malfunzionamento del componente, bensì come un progressivo deterioramento delle sue prestazioni nel tempo. Ad esempio, effetti quali l'Nbti (Negative Bias Temperature Instability) possono produrre un graduale innalzamento nel tempo della tensione di soglia dei transistor Pmos, che porta alla riduzione della velocità di switching dei gate logici, e all'effetto di Hot Carrier Injection, che altera nel tempo il voltaggio di soglia delle apparecchiature Nmos. Un altro meccanismo di malfunzionamento che si manifesta nel tempo è il cosiddetto Soft Breakdown, che si assomma agli effetti di degrado del gate oxide breakdown. Un'importante applicazione dei controlli di affidabilità consiste nel verificare che, ovunque siano presenti nell'apparecchiatura potenziali vulnerabilità, vi siano anche dei circuiti di protezione dalle scariche elettrostatiche Esd, indipendentemente dal fatto che essi fossero già previsti nello schema e nella netlist oppure no. Al fine di garantire la robustezza del progetto, il tool di controllo dell'affidabilità deve essere in grado di andare oltre semplici logiche di verifica di tipo schematic-to-layout o netlist-to-layout, e riconoscere autonomamente i punti in cui sono necessari elementi di protezione Esd, sulla base di informazioni combinate provenienti sia dalla netlist che dalla topologia del layout. Negli IC dotati di più domini di potenza sono necessarie ulteriori precauzioni da eventi Esd. Il riutilizzo di IP può comportare la necessità di regole Esd più robuste, per evitare malfunzionamenti riconducibili a circuiti non correttamente accoppiati allo stadio di integrazione di sistema. Tale possibilità è piuttosto frequente, ad esempio, ogniqualvolta un blocco IP viene adattato ad un diverso nodo di processo o dominio di potenza. Un altro caso in cui il riutilizzo di IP può compromettere l'affidabilità complessiva del chip è quello connesso all'introduzione di domini di potenza a voltaggio inferiore. Spesso, per abbassare le soglie di voltaggio per circuiti di potenza inferiore, si ricorre a un assottigliamento dello strato di ossido di un transistor. Tale intervento senza dubbio produce significativi benefici in termini di voltaggio e di potenza, ma al contempo introduce delle aree di potenziale rischio, ad esempio nel caso in cui i gate con ossido assottigliato siano connessi a linee con particolari tensioni. Per evitare che i gate si possano progressivamente deteriorare nel tempo, conducendo ad un degrado delle performance, è necessario che la linea di voltaggio venga scelta con cura. In un'implementazione precedente, infatti, il gate potrebbe essere stato connesso a un voltaggio che si rivela troppo elevato per l'uso corrente. Perché l'integrazione dei blocchi IP fisici avvenga con successo, è necessaria una piena conoscenza sia della gerarchia progettuale che della struttura dei domini di voltaggio e dei vincoli di voltaggio delle celle. La gerarchia del progetto entra in gioco anche quando viene applicato un determinato insieme di regole alle interconnessioni ed alle frame di pad dello strato superiore, mentre vengono usate regole differenti tra i blocchi che attraversano molteplici domini di potenza.

L'importanza della programmabilità del tool

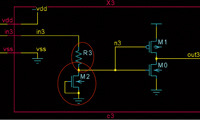

Poiché l'affidabilità diventa sempre più determinante per la robustezza dei prodotti, i progettisti e gli ingegneri sono alla continua ricerca di nuovi controlli che consentano un verifica elettrica accurata. Tuttavia, non esistendo un insieme predefinito di controlli “standard”, diventa cruciale che il tool di affidabilità utilizzato sia facilmente programmabile, perché gli utenti possano adattarlo rapidamente a qualsiasi nuovo controllo non appena ciò si riveli necessario. Per mostrare in quale modo i progettisti possono utilizzare i nuovi strumenti per la verifica dell'affidabilità, viene di seguito illustrato un controllo di esempio effettuato mediante il prodotto Calibre Perc di Mentor Graphics, utilizzabile per individuare errori di progetto non rilevati dai tool tradizionali di PV. Tipicamente, Calibre Perc viene usato o in abbinamento a regole standard fornite dalla fonderia, oppure con regole custom create da un apposito team di progetto. Gli utenti possono inserire controlli di affidabilità per la verifica con Calibre Perc a livello di cella, di blocco e full-chip direttamente all'interno del proprio flusso di progetto, in quanto il tool fa parte della piattaforma integrata Calibre. La possibilità di combinare regole espresse sia in SVRF che nel linguaggio TVF, basato su TCL, su tutto lo spettro di applicazioni assicura agli utenti la flessibilità necessaria per soddisfare le esigenze specifiche e mutevoli dei team di progetto, garantendo al contempo la compatibilità con tutte le fonderie. Nella Fig. 3 viene mostrato un circuito contenente dei gate Pmos e Nmos thin-oxide, ovvero ad ossido sottile, con connessioni sia dirette che indirette ai domini di potenza VDD2 e VSS2. Una connessione indiretta può avvenire tramite un altro transistor, un diodo, una resistenza, oppure altri elementi circuitali. Tali connessioni formano spesso la base di percorsi “mancati”, non prontamente identificati durante le revisioni del progetto. Ciò risulta particolarmente vero in quei casi in cui il percorso indiretto transita attraverso un circuito posto altrove nella gerarchia del progetto, magari in una posizione non molto ovvia. Le connessioni power locali del sottocircuito in esame (VDD/VSS) vengono mostrate nel contesto del progetto complessivo. Viene quindi evidenziata la necessità di valutare nuovamente le connessioni esterne ad un blocco IP altrimenti considerato già valutato.

Per identificare i gate thin-oxide a rischio, i progettisti provvedono a definire in Calibre Perc un controllo di questo tipo (qui espresso in pseudo-codice, per semplicità):

1. Identificare i domini di potenza del progetto

2. Identificare i domini di potenza “non sicuri” per i gate thin-oxide

3. Identificare gli specifici tipi e sotto-tipi di device corrispondenti a dispositivi Mos thin-oxide

4. Controllare le relative connessioni di pin “source”, “drain”, o “bulk” di questi dispositivi Mos thin-oxide ai domini di potenza considerati critici

a. a. Valutare sia i percorsi diretti che quelli indiretti

b. b. Marcare con un errore le connessioni dei Mos thin-oxide ai domini di potenza “non sicuri”.

In sistemi complessi è frequente la presenza di molteplici domini di potenza, che richiedono la definizione di regole molto elaborate per la determinazione di quali domini possano essere considerati sicuri, ed in quali condizioni.

La verifica delle connessioni dei pin bulk è particolarmente importante per determinare se un circuito sia esposto alle problematiche di affidabilità nel tempo appena menzionate. Una connessione bulk errata può rendere questo gate Pmos vulnerabile a problemi di tipo Nbti (Negative Bias Temperature Instability), dovuti ad un elevato voltaggio di bulk. Per affrontare le sfide di affidabilità e di resa funzionale imposte dagli avanzati e complessi progetti odierni di IC, sono necessarie nuove strategie di verifica. Fino ad ora, le soluzioni di Eda hanno rivelato ampi divari nella capacità di rispondere alle esigenze connesse alla verifica elettrica e circuitale. La protezione dai rischi di affidabilità derivanti dall'attraversamento di molteplici domini di potenza, o dalle catastrofiche conseguenze di fenomeni di Esd, può implicare enormi impatti sulla resa e sull'affidabilità complessiva. La verifica di affidabilità rappresenta una soluzione che affronta il problema della verifica del circuito sia dal punto di vista geometrico che dal punto di vista elettrico. Ciò consente ai progettisti di implementare nuove regole di verifica e di garantirne il rispetto, risolvendo problematiche di affidabilità la cui soluzione mediante gli approcci convenzionali si rivela sia difficile che onerosa in termini di tempo.