Nella progettazione di una scheda a circuito stampato uno degli elementi fondamentali per il corretto funzionamento del sistema è la rete di alimentazione o Pdn (Power distribution network) dei vari circuiti integrati montati sulla scheda costituito principalmente dai piani di alimentazione e dai piani di massa. Se la rete non è progettata correttamente si possono verificare malfunzionamenti o problemi di compatibilitá elettromagnetica come fenomeni di radiazione o suscettibilitá. Il circuito da analizzare consiste nei seguenti elementi fondamentali:

- il modulo regolatore di tensione o Vrm (Voltage regulating module) è l’elemento che alimenta il sistema e deve essere in grado di provvedere la corrente necessaria al corretto funzionamento della scheda alle varie tensioni necessarie;

- Il carico o Sink, corrisponde a uno dei circuiti integrati che assorbono corrente;

- la rete di alimentazione o Power Rail è la pista che porta la tensione di alimentazione dal modulo regolatore al carico;

- la rete di massa o Ground Rail è la parte del circuito che funge da percorso di richiusura della corrente dal carico al modulo regolatore.

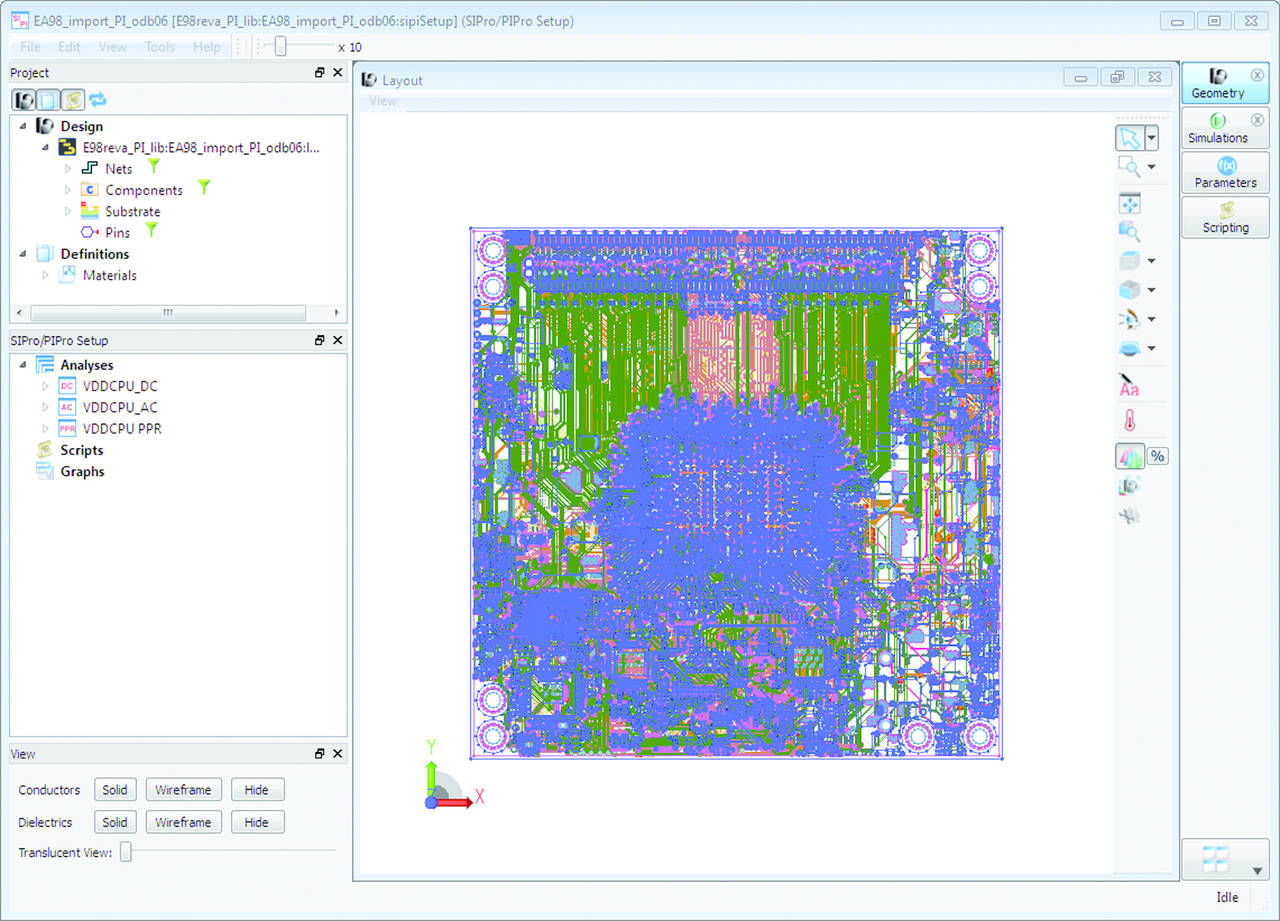

Il simulatore PIPro

Di seguito viene descritta una serie di analisi effettuate su una scheda di tipo embedded Pc in formato Com Express, formato industriale di ampia diffusione ad alte prestazioni e ingombri ridotti, sviluppata dalla società Seco di Arezzo. Il componente principale della scheda è un processore R-Series Merlin Falcon a 3.2 GHz di Amd, che ha un assorbimento massimo di picco di circa 51 A sulla vcore in performance mode e pertanto necessita di un’attenta progettazione della rete di alimentazione. Per l’analisi power integrity è stato utilizzato il nuovo simulatore PIPro di Keysight Technologies. Questo simulatore è basato sul metodo di analisi elettromagnetica degli elementi finiti ottimizzato per permettere l’analisi di schede di dimensioni medio-grandi ad alto numero di strati in tempi ragionevoli e con un alto livello di precisione. La figura in apertura mostra la scheda sbrogliata dopo che è stata importata nell’ambiente Advanced Design System di Keysight EEsof EDA.

L’analisi PI-Dc

Iniziamo dal tipo di analisi piú semplice (PI-Dc) che consiste nel calcolo delle cadute di tensione statiche in corrente continua e delle densitá di corrente e potenza associate nell’insieme della rete di alimentazione. Questa analisi permette di individuare quali sono i circuiti integrati, i pin dei connettori e i via di richiusura di massa che sono attraversati dal maggior livello di corrente.

Se la caduta di tensione nel circuito di alimentazione supera un determinato valore la tensione di alimentazione del circuito integrato non arriverá al livello minimo richiesto per il suo corretto funzionamento e risultare nello spengimento del circuito, in fenomeni di reset oppure in malfunzionamento a livello della logica interna del dispositivo. Densitá di corrente eccessive nelle piste di alimentazione generano temperature elevate che possono risultare in delaminazioni del circuito stampato e in casi estremi in surriscaldamento e talvolta anche in incendio della scheda. Passaggi tra differenti strati che portano correnti eccessive possono arrivare a fondere e interrompere il circuito. La simulazione statica in corrente continua (PI-Dc) genera vari risultati tra i quali alcuni in cui la tensione minima nella zona corrisponente alla connessione della Cpu raggiunge un valore minimo di circa 1,1 V compreso nella tolleranza massima di ± 120 mV rispetto ai 1,2 V di tensione di alimentazione nominale della Cpu.

È anche disponibile un report dettagliato che include misure quantitative di tensione sia per quanto riguarda la Cpu che il modulo regolatore e misure di tensione e corrente sulle piazzole di connessione e nei via, con indicazione di eventuale superamento dei valori massimi stabiliti.

L’analisi PI-Ac

Il secondo tipo di analisi (PI-Ac) ha come obiettivo quello di garantire il mantenimento del livello minimo di tensione di alimentazione in condizioni dinamiche, cioé una volta che il dispositivo è in funzionamento e il suo consumo di corrente varia nel tempo secondo il tipo e la sequenza di operazioni svolte dalla Cpu. La frequenza di clock del processore R-Series è di 3,2 GHz e quindi il contenuto armonico della corrente di alimentazione è elevato. La simulazione elettromagnetica del circuito di alimentazione di conseguenza viene configurata per coprire tutto lo spettro da Dc fino a 3 GHz. Al modello cosí ricavato vengono poi aggiunti automaticamente i modelli equivalenti del regolatore di tensione, del carico e dei condensatori di disaccoppiamento. Questi ultimi vengono collegati tra la rete di alimentazione e quella di massa e il loro piazzamento e valori di capacitá costituiscono i principali parametri a disposizione del progettista per ottimizzare il funzionamento del sistema. Da un punto di vista operativo il risultato principale della simulazione completa consiste nel grafico riportato in Fig. 6 in cui viene riportato il valore dell’impedenza vista dalla Cpu (asse Y) rispetto alla frequenza (asse X), ambedue in scala logaritmica. In questo grafico sono tracciate due curve, una con i condensatori di disaccoppiamento sconnessi (curva rossa), e la seconda con i condensatori connessi. I modelli utilizzati per i condensatori includono i valori parassiti di induttanza e resistenza. Si nota come il valore generale di impedenza nel secondo caso sia inferiore e come il picco di risonanza sia ridotto in ampiezza (da circa 22 Ohm a circa 5 Ohm) e spostato a frequenza superiore (da circa 230 MHz a più di 900 MHz). In questo caso non sono disponibili specifiche precise sul livello di impedenza massimo consentito rispetto alla frequenza quindi è stata calcolata un’impedenza di target data dal rapporto tra la massima tensione di ripple consentita e la corrente transitoria massima stabilita dal costruttore della Cpu, che da un valore di circa 150 mΩ. Questo valore viene rispettato fino oltre i 100 MHz, dopo i quali si cerca di spostare più in alto possibile le eventuali risonanze.

L’analisi PI-Ppr

L’ultima analisi di tipo Power Integrity che viene effettuata è la mappatura sulla scheda delle risonanze dei piani di alimentazione, detta analisi PI-Ppr (Power plane resonance) che consente poi di piazzare eventuali condensatori di disaccoppiamento aggiuntivi nelle posizioni ottimali per sopprimere le risonanze residue. Eseguendo queste analisi e applicando le dovute correzioni la scheda è rientrata rapidamente nelle specifiche di impedenza stabilite in sede di progetto. L’utilizzo del simulatore PIPro, grazie ai tempi di simulazione contenuti (la simulazione più lunga ha avuto una durata di circa 1h15’) e all’alto livello di precisione ha permesso un risparmio significativo nei tempi di progettazione e di passare rapidamente alla fase di produzione della scheda.

Una suite di simulazione completa

SIPro e PIPro di Keysight completano una suite di simulazione formata da ADS ed EMpro, che permette al progettista di High Speed Digital di spaziare su tutte le problematiche poste da un odierno sistema embedded industriale. La velocità di utilizzo e l’interazione con gli altri tool disponibili fanno di SIpro e PIpro l’approccio più veloce e intuitivo alle problematiche che gli ingegneri che si occupano di Signal Integrity devono fronteggiare tutti i giorni.