Il mercato dei circuiti integrati è governato da esigenze sempre più stringenti dal punto di vista del time-to-market. Per far fronte a questa necessità, Ansys RedHawk offre una piattaforma di simulazione affidabile, in grado di fornire il rumore dovuto alla distribuzione di potenza sul silicio che alimenta i circuiti integrati a basso consumo ed elevate prestazioni. Ansys RedHawk calcola la capacità equivalente del chip e fornisce l’ottimizzazione, accuratezza di calcolo validata sul silicio e copertura sign-off richieste per i circuiti integrati, in particolare per applicazioni di elettronica mobile a basso consumo, networking, consumer e automotive. La soluzione rappresenta uno standard tra le soluzioni sign-off ed è parte integrante di ogni flusso di fabbricazione dei circuiti integrati, incluso il nodo tecnologico rappresentato dalla tecnologia FinFet inferiore ai 20 nm. Incrementando l’intensità di corrente e riducendo i margini di rumore sulle tecnologie di processo avanzate, modellare e simulare accuratamente il comportamento reale del chip risulta un fattore critico. La piattaforma Ansys RedHawk considera l’impatto del rumore del package e del Pcb sulla potenza dei circuiti integrati e consente un’analisi della potenza di rumore e sign-off per il package, il Pcb e l’intero sistema, al fine di assicurare che si ottenga il margine di rumore più stretto senza spreco di risorse o rischi di fallimento.

La piattaforma Ansys RedHawk

La piattaforma Ansys RedHawk è un’architettura scalabile e una tecnologia di progettazione avanzata che assicura capacità full-chip con accuratezza sign-off. Queste caratteristiche sono necessarie perché la progettazione sta diventando sempre più complessa con nodi di tecnologia minori. Inoltre, la piattaforma è rispondente alle richieste di produzione. Ansys RedHawk è uno standard scelto dai professionisti della progettazione in tutto il mondo come soluzione sign-off in quanto costituisce un ambiente integrato per il design, compresa la validazione IP in un contesto SoC, una metodologia completa Rtl-to-Gds power sign-off, un design di package/Pcb chip-aware e sign-off package/Pcb-aware chip. Il feedback termico e l’analisi di layout package integrato costituiscono un ulteriore valore aggiunto per il software.

Capacità e performance elevate

Ansys RedHawk offre la capacità necessaria per simulazioni full-chip senza compromettere l’accuratezza sign-off per il drop di tensione dinamica, l’elettromigrazione e l’analisi di scariche elettrostatiche. La combinazione di un database riprogettato, numerosi eseguibili e solutori potenziati consente la simulazione di miliardi di nodi e di matrici di network Rlc, così come di modelli di package completi e accoppiati elettricamente. Ottimizzando la progettazione e la simulazione dei componenti necessari per l’accuratezza sign-off, Ansys RedHawk migliora le performance sia in termini di turnaround totale che di footprint di memoria, mentre genera risultati validati su silicio di tecnologie di design sub-20 nm. Sono state incorporate tecnologie addizionali per rispondere al numero e alla complessità crescenti delle verifiche EM-rule. Per design di grosse dimensioni, specialmente quelli realizzati con tecnologie FinFet, Ansys RedHawk impiega il processo distribuito su processori in cui la simulazione è distribuita su diversi processori in un cluster privato. Questa caratteristica consente di simulare 100 M+ istanze o 2B+ nodi di design mantenendo l’accuratezza della simulazione sign-off. L’architettura proprietaria Dmp consente a ciascuna porzione distribuita di design di essere simulata nel contesto dell’intero chip inclusi package e Pcb.

Accuratezza sign-off silicon validated

Ansys RedHawk è certificato FinFet da industrie leader del settore per l’integrità IR/DvD, Em e Esd. Il software utilizza la libreria di alimentazione Apache e il Custom Macro Model per incorporare forme d’onda di corrente di commutazione, parametri parassiti RC a livello di dispositivo per la simulazione completa transient del chip a una risoluzione di picosecondi. Questi modelli sono potenziati per soddisfare le esigenze della progettazione più avanzata. Inoltre, Ansys RedHawk simula contemporaneamente i domini di alimentazione e di ground presenti nel SoC attuale per prevedere accuratamente la corrente e la tensione di ogni cella di design. Per progetti sub 20 FinFet, Ansys RedHawk amplia i suoi modelli, la capacità di estrazione e di analisi per supportare strati di metallo speciale e strutture complesse, così come prototipi, resistenze verticali e modelli double patterning. Queste capacità assicurano che i SoC progettati per le più innovative tecnologie soddisfino le esigenze IR/Dvd. Un sign-off accurato dell’attuale SoC a bassa potenza e alte performance richiede l’inclusione di modelli dettagliati IP e parassiti package/Pcb. Ansys RedHawk assicura flessibilità nei modelli di numerose Ips basate su simulazioni dettagliate con Ansys Totem e analizza accuratamente l’effetto di package e parametri parassiti del Pcb sulla corrente dinamica con Ansys RedHawk Cpa, una feature di coanalisi integrata chip-package. Quest’ultima mappa il design del package al suo die corrispondente attraverso la connettività fisica pin-to-pin consentendo il merging di un’intera rete di parametri parassiti del package distribuita con un network on-die di distribuzione di potenza.

Sign-off ad elevata affidabilità

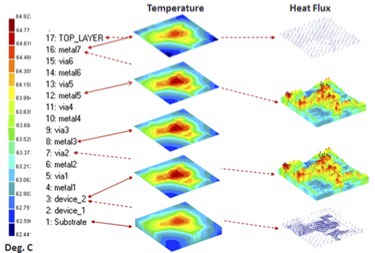

Le problematiche relative a Em e Esd diventano ancor più critiche quando il design si sposta al di sotto dei 20 nm. Ansys RedHawk fornisce supporto completo per analisi power/ground e linee di segnale Em, analizzando accuratamente le violazioni Em e minimizzando i falsi positivi. Le sue tecniche proprietarie di estrazione dei flussi di corrente aiutano a creare e simulare reti Rlc in modo da fornire risultati di qualità sign-off per ogni aspetto del design. Ansys Pathfinder, parte della piattaforma Ansys RedHawk, supporta analisi di integrità SoC-level Esd conferendo connettività e controlli di errore interconnessi per tutti i flussi di corrente da un evento Esd. In progetti FinFet la sfida principale è il surriscaldamento, che rende ancora più complesse le problematiche Em ed Esd. Il sistema Ansys chip-package per l’analisi del flusso termico incorpora i dati del chip con il package e il system per generare profili termici on-chip accurati. Ansys RedHawk consente di fare analisi termiche Em ed Esd incorporando questi profili termici.

Maggiore copertura per la chiusura power noise

Identificare i punti caldi di design in assenza di vettori di input è un fattore critico per la copertura di problematiche di power integrity e affidabilità. Ansys RedHawk supporta un motore di simulazione dinamico VectorLess che genera automaticamente scenari di switching con o senza limiti specificati dall’utente per una copertura completa del chip. Modi addizionali VectorLess supportati da Ansys RedHawk includono Power Transient, Frequency Aware e VectorLess Scan. RH supporta anche numerosi motori di simulazione che consentono la chiusura di power noise da Rtl a Gds. I motori VectorLess Rtl Vcd e Vcd gate-level possono essere simultaneamente coinvolti nel design consentendo applicazioni mixed-mode per simulare ogni blocco con qualsiasi input di vettore dati disponibile per ciascun blocco. Per esempio, se un blocco ha un gate-level Vcd e un altro ha vettori Rtl, Ansys RedHawk usa le attività di rete da questi vettori per i blocchi rispettivi e usa i motori VectorLess per il resto della progettazione per generare una configurazione di switching.