Per molti anni il processo di debugging, durante le fasi di progettazione e di verifica degli Asic e degli Fpga, è consistito sostanzialmente nell’indagine della struttura e del codice sorgente del progetto mediante forme d’onda che ne mostrassero l’attività al passare del tempo, a fronte di stimoli di input indotti tramite i testbench. I progetti odierni, tuttavia, sono diventati enormemente più complessi, essendo spesso composti da più sottosistemi, di grandi dimensioni e ricchi di IP (sia di tipo legacy che acquisita), e con la presenza di processori multipli in cui viene eseguito software embedded. Data la complessità delle interazioni esistenti, un debugging efficace spesso richiede l’impiego di specialisti molto esperti, che abbiano dimestichezza con tutti i componenti presenti. Con gli sforzi effettuati per potenziare la modularità e la riusabilità nelle attività di testing, i testbench e gli input di stimolo per tali progetti e blocchi IP hanno subito un’evoluzione, trasformandosi da semplici test specifici in veri testbench reattivi ed auto-verificanti, spesso realizzati mediante linguaggi object-oriented e basati sulle classi, come ad esempio SystemVerilog. Secondo uno studio sulla verifica condotto dal Wilson Research Group, gli ingegneri impegnati nella progettazione e nella verifica oggi spendono più del 36% del proprio tempo nelle attività di debugging, e tale percentuale è ulteriormente in crescita.

Affrontare la sfida del debugging

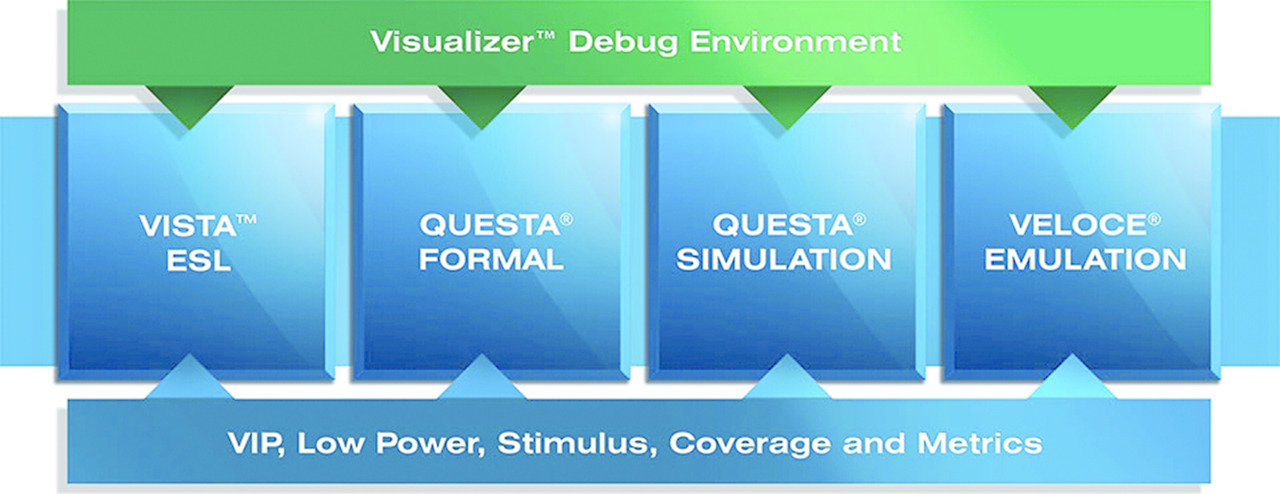

L’ambiente di debugging Visualizer di Mentor Graphics affronta questa sfida offrendo un debugger caratterizzato da alta capacità ed elevate prestazioni, in grado di scalare dalla simulazione all’emulazione, pur rimanendo intuitivo e semplice da utilizzare per le attività quotidiane, dotato di molteplici funzionalità automatizzate per la ricerca rapida dei bug ai livelli Rtl e dei gates, nonché basato sul linguaggio a classi SystemVerilog e compatibile con Uvm, il tutto per consentire di ridurre i tempi complessivi del debugging, perfino sui più complessi sistemi SoC ed Fpga odierni.

Interfaccia utente intuitiva, potenti funzionalità per il debugging dei progetti

L’ambiente di debugging Visualizer è stato concepito per essere veloce e semplice da usare, per supportare le attività nelle quali gli ingegneri addetti alla progettazione ed alla verifica spendono circa l’80% del proprio tempo: il tracing e la navigazione all’interno del progetto, al fine di comprenderne i dettagli. Il layout dello strumento, i suoi menu ed i suoi pulsanti sono intuitivi, e tutte le sue finestre sono sincronizzate rispetto al tempo. L’esplorazione del progetto e delle sue connessioni ai driver ed ai reader richiede solo un clic del mouse, ed è agevolato dalla presenza di una funzione di navigazione avanti/indietro. L’attivazione della funzione di tracing mostra quale codice sia attualmente in esecuzione. Appoggiate su questa intuitiva piattaforma di base vi sono poi nello strumento numerose potenti funzioni di automazione, che assistono nella comprensione del progetto e delle funzionalità che esso implementa. Tra queste, una vista denominata TimeCone, che automatizza il tracing e la visualizzazione delle cause di un evento (come ad esempio un evento X), risalendo fino alla sua origine anche attraverso molteplici clock; nonché la Ricerca Biometrica, una modalità semplificata per ricercare ed evidenziare tutti i punti in cui uno specifico valore ricorrente appare all’interno dell’intero progetto.

Debugging unificato simulazione ed emulazione

L’ambiente di debugging Visualizer è stato interamente costruito, fin dalle sue fondamenta, per garantire le massime prestazioni e la massima capacità. Supporta il debugging mediante dati provenienti non solo dalla simulazione nell’ambiente Questa, bensì anche mediante una perfetta integrazione con l’emulazione operata nel tool Veloce o con il flusso di accelerazione della simulazione TBX di Veloce/Questa: in quest’ultima combinazione, il testbench (Uvm, basato su classi, ecc.) viene eseguito in QuestaSim, mentre l’Rtl viene eseguito all’interno dell’emulatore Veloce. L’utente continua comunque a operare all’interno di un unico ambiente di debugging, nel quale i dati provenienti dalle diverse fonti vengono perfettamente integrati e resi disponibili insieme per il debugging, con tutte le stesse funzionalità presenti in un tipico ambiente di pura simulazione. In aggiunta, nel debugger Visualizer è presente una funzione di caricamento incrementale on-demand del progetto e delle forme d’onda, che consente di caricare in memoria solo i moduli necessari, e solo i dati delle gerarchie e delle forme d’onda corrispondenti a determinati intervalli temporali. Questa funzionalità rende possibile una scalabilità dinamica dell’ambiente di debugging, che riesce in questo modo a gestire gli enormi volumi dei dataset tipici dell’emulazione, presentando comunque all’utente dei dati on-demand e mantenendo dei tempi di avvio estremamente rapidi. L’integrazione di Veloce con il debugger Visualizer consente anche la visualizzazione delle annotazioni e la navigazione nei percorsi della logica sintetizzata, all’interno del contesto dell’ambiente di progettazione dell’Rtl.

Esclusiva funzionalità per il debugging avanzato dei testbench

L’utilizzo delle pratiche di programmazione class-based ed object-oriented all’interno della verifica ha senza dubbio migliorato la riusabilità, la testabilità e la produttività, seppur non senza introdurre alcune nuove sfide per quanto riguarda il debugging. I moderni testbench basati su Ovm/Uvm e le altre metodologie basate sulle classi impongono infatti un approccio al debugging che è più simile a quello utilizzato nello sviluppo del software, rispetto a quello tradizionale di analisi time-based a livello dell’Rtl e dei gate, comunemente impiegato dai progettisti di Asic e di Fpga. L’ambiente Visualizer possiede funzionalità esclusive per la visualizzazione e il debugging dei componenti basati sulle classi e Uvm, in modalità post-simulazione. Il browser delle gerarchie supporta la piena rappresentazione della gerarchia dei componenti Uvm, nonché la navigazione all’interno del codice sorgente con tutte le annotazioni, in modo da consentire una facile visualizzazione dei valori del testbench nel tempo. Le viste degli schemi Uvm mostrano chiaramente la connettività dei testbench e le interfacce di connessione al Dut. L’ambiente di debugging Visualizer è anche in grado di comprendere la sottostante architettura Uvm interna e di semplificarne la rappresentazione per l’utente, presentando solo le informazioni vitali, filtrate attraverso l’ambiente Uvm. Supporta inoltre l’utilizzo di un insieme completo di annotazioni e di tool-tip all’interno del codice sorgente, per consentire l’agevole esplorazione dei contenuti di qualsiasi handle di una classe o di un oggetto Ovm/Uvm, così come l’aggiunta di classi e oggetti alla forma d’onda, per mostrane i valori nel tempo. Oltre agli handle delle classi e ai segnali, il debugger Visualizer supporta anche il debugging a livello di transazione, sia nella vista delle forme d’onda che all’interno di un’esclusiva vista “transaction stripe”, per consentire una facile ricerca dei dati all’interno di insiemi molto ampi, legati a transazioni complesse.