Gli operatori delle reti cellulari cercano di ridurre i costi in modo significativo, sforzandosi di aumentare la propria copertura e la capacità di rete attraverso una banda estesa, un numero crescente di antenne Mimo, più siti cellulari e nuove frequenze di trasmissione. Allo stesso tempo, questi operatori di rete perseguono una riduzione dei costi acquistando apparecchiature radio che assicurano livelli migliori di efficienza e di integrazione. I produttori che forniscono apparecchi per le infrastrutture wireless a questi operatori di rete sono alla ricerca di soluzioni progettuali a livello di sistema che forniscano livelli superiori di integrazione, prestazioni superiori e una maggiore flessibilità, riducendo al contempo il consumo di potenza e il costo di acquisto. I produttori di apparecchiature devono raggiungere tutti questi obiettivi riducendo al contempo il time-to-market.

Con l’introduzione delle tecnologie Tdd-Lte e Fdd-Lte, in corso in molte parti del mondo, si è osservato un salto di qualità nelle caratteristiche richieste per le apparecchiature e nei requisiti di prestazioni rispetto ai prodotti con interfaccia aria lanciati in precedenza. La configurazione più comune usata per l'introduzione delle tecnologie Cdma2000 e Wcdma 3G era una radio 2x2 da 20 MHz, ma tale configurazione da allora si è evoluta verso configurazioni che forniscono ampiezze di banda superiori e supportano più bande di frequenza. I produttori stanno ora sviluppando comunemente radio Mimo in grado di fornire fino a 100 MHz di banda utilizzabile. Queste nuove configurazioni fanno tipicamente uso matrici di antenne Mimo 4x4 e 8x8.

L’evoluzione delle radio a banda ultra larga

Lo sviluppo di queste radio a banda ultra larga consentirà agli operatori di rete di mettere a punto radio singole in grado di supportare più bande di frequenza di interesse - ad esempio 1800, 1900 e anche 2100 MHz in futuro - consentendo di ottenere un numero inferiore di radio remote montate in cima alla torre, il che a sua volta riduce i costi. Questa evoluzione non solo abbatte in modo significativo i costi di capitale per le apparecchiature, grazie all'uso di un numero inferiore di radio, ma riduce anche in modo significativo i costi operativi e i costi di locazione dei siti in cui sono posizionate le antenne, grazie alla riduzione del carico del vento e alla diminuzione del carico legato al peso totale sulla torre.

Una radio 8x8 da 100 MHz richiede una potenza di calcolo di elaborazione 20 volte superiore rispetto ad una radio 2x2 da 20 MHz. Quando si considerano i requisiti di elaborazione digitale e analogica per un simile apparecchio radio, è difficile immaginare come potrebbero essere realizzati i prodotti soddisfacendo al contempo i vincoli di tipo meccanico, termico e di costo imposti dalle radio remote raffreddate in modo passivo. È richiesta ovviamente la continua evoluzione di nuove generazioni di IC digitali e analogici. Si considerino a titolo di esempio i requisiti a livello di sistema per la realizzazione di una radio 8x8 da 100 MHz. In una radio cellulare 8x8, le dimensioni che definiscono i dispositivi Fpga richiesti dovevano includere il numero delle antenne, l’interfaccia aria, il numero delle portanti e la banda istantanea. Il numero di antenne definisce il numero richiesto di connessioni Dac e Adc. La banda istantanea della radio definisce la frequenza di campionamento e di conseguenza determina la velocità e il numero di porte SerDes richieste per connettere le risorse di elaborazione digitale dei segnali all’interno dell’Fpga con i Dac e gli Adc.

Progressi nella conversione dati

I convertitori di dati sono stati l’oggetto di progressi significativi nel coso degli ultimi anni, con numerosi produttori che ora offrono più Dac e Adc in un singolo alloggiamento, connessi alla circuiteria di elaborazione della radio digitale attraverso un’interfaccia Jesd204B. Lo standard di interfaccia Jesd204B sostituisce le più tradizionali interface parallele Lvds usate in precedenza con porte SerDes ad alta velocità in grado di operare a 12,5 Gbps. Le interfacce Jesd204B riducono in modo significativo il numero delle connessioni richieste fra i Dac e gli Adc e la circuiteria di elaborazione del blocco di interfaccia digitale di ingresso. La conseguenza è un numero inferiore di strati Pcb e una potenza di interfaccia ridotta. Per di più, questi convertitori Jesd204B stanno ora diventando sempre più integrati; essi inglobano interi sottosistemi di elaborazione RF verso l’ingresso o verso l’uscita, producendo IC Rf ad alte prestazioni che includono i Dac, gli Adc, i filtri e i modulatori necessari per creare blocchi di interfaccia analogici di ingresso altamente integrati e ad alte prestazioni. Oltre a determinare il numero dei transceiver SerDes richiesti, la banda di una radio cellulare e il numero delle antenne stabiliscono anche la quantità di logica e di risorse Dsp richieste per elaborare algoritmi, inclusi gli algoritmi di conversione verso frequenze superiori (Duc) e verso frequenze inferiori (Ddc). Gli algoritmi Duc e Ddc si prestano molto bene per realizzazioni su Fpga, perché consentono ai clienti nel settore delle reti di mettere a punto gli algoritmi, secondo le proprie necessità, senza dover apportare modifiche all’hardware. Due ulteriori algoritmi comunemente usati sono la riduzione del fattore di cresta e la pre-distorsione digitale, che migliorano l’efficienza dell’uscita radio dell’amplificatore di potenza. In base alle risorse Dsp richieste per mettere a punto una radio a banda larga e al numero di Serdes richiesti per comunicare con otto antenne, un metodo economico per realizzare una radio cellulare usando gli Fpga di Xilinx di attuale generazione, consisterebbe nel suddividere l’elaborazione dell’algoritmo fra due dispositivi. Questo partizionamento di sistema crea efficacemente due radio 4x4 da 100 MHz. Un sottoprodotto di ciò è la suddivisione dell’alimentazione in modo uniforme fra due dispositivi digitali, semplificando i vincoli del progetto termico e semplificando gli aspetti meccanici del progetto.

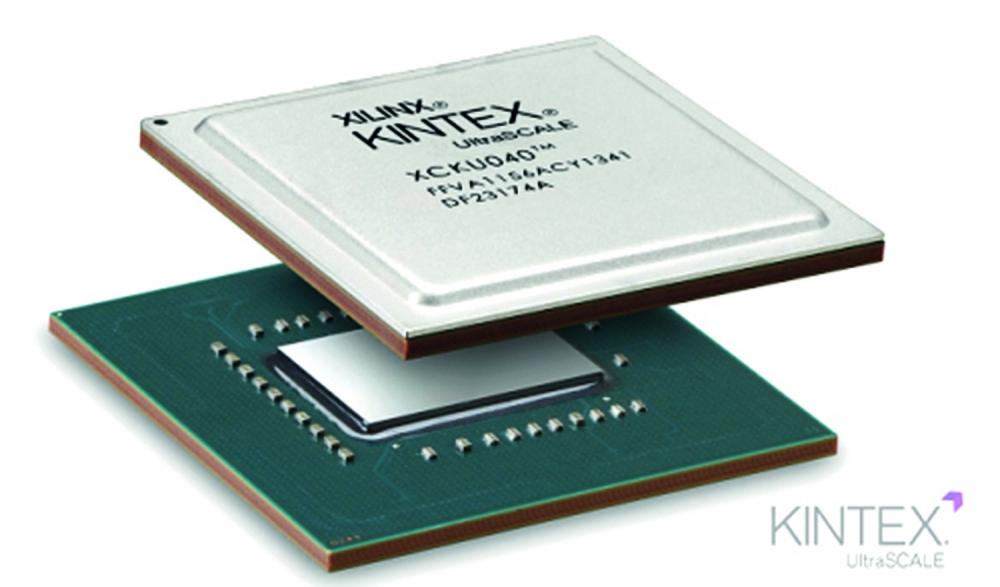

Dispositivi UltraScale Kintex

Tuttavia, questa partizione a livello di sistema non è più necessaria se si usano i dispositivi UltraScale Kintex di Xilinx, che presentano una capacità Dsp, un numero superiore di porte SerDes e consumi significativamente inferiori.

Infatti, l’architettura UltraScale è stata altamente adattata alle esigenze di questo tipo di progetto radio. La Ram a blocchi e la Ram Lut (Look up table) altamente efficienti dell’architettura UltraScale e i suoi blocchi Dsp DSP48E2 ottimizzati si combinano in modo efficiente per creare molti tipi di filtri necessari per gli algoritmi Duc, Ddc, Cfr e Dpd per l’elaborazione dei segnali. La matrice logica programmabile dell’architettura UltraScale e la memoria su chip consentono di mettere a punto microprocessori sintetizzabili ad alte prestazioni, che possono essere usati con l’accelerazione hardware per realizzare unità di calcolo Dsp altamente scalabili e con basso coefficiente di ingombro. Gli Fpga UltraScale possono raggiungere velocità di clock di oltre 491 MHz, il che permette di sfruttare la multiplazione a divisione di tempo per ridurre ulteriormente la quantità di area su chip dedicata all’elaborazione dei segnali, pur mantenendo i bassi consumi di potenza di un progetto radio basato su Fpga. Di conseguenza, una radio 8x8 da 100 MHz può essere realizzata solo con un Fpga UltraScale Kintex. Per mettere a punto una radio complessa di questo tipo in un singolo dispositivo, l’alimentazione globale deve essere considerevolmente limitata per ridurre il calore generato. Gli Fpga basati sull’architettura UltraScale di Xilinx sono stati adattati per il funzionamento a basso consumo in diversi modi. Innanzitutto, il consumo di potenza statica di due Fpga da 28 nm è stato sostituito da un solo Fpga da 20 nm. In più, un’attenta progettazione ha ridotto in modo significativo i consumi di potenza dinamica della matrice in logica programmabile dei dispositivi e dei transceiver SerDes. È necessario un numero inferiore di blocchi Dsp per la realizzazione di filtri digitali basati su operazioni Mac (moltiplicazione/accumulo) complesse. La diminuzione del numero richiesto di blocchi Dsp riduce la potenza dinamica e l’area necessaria per mettere a punto algoritmi Duc, Ddc, Cfr e Dpd. Il risultato, a livello di sistema, è una riduzione dell’8% dei costi per coppia di unità di trasmissione/ricezione e una riduzione dei consumi di potenza di più del 31% rispetto a una realizzazione basata su un dispositivo di generazione precedente. È possibile ottenere ulteriori risparmi di costo a livello di sistema grazie al numero modesto di strati Pcb richiesti e alla complessità ridotta dell’alimentazione. Un alimentatore di dimensioni inferiore e un sistema di raffreddamento più piccolo e meno complesso riducono inoltre il peso del sistema radio remoto e le dimensioni necessarie per l’alloggiamento, che abbattono ulteriormente la distinta materiali e i costi operativi.