La tecnologia evolve in modo sempre più rapido. Nel mondo delle connessioni a elevata velocità le reti Ethernet operanti a 100 Gbps stanno iniziando a subentrare a quelle operanti a 40 Gbps, mentre il lavoro dei comitati Ieee per la definizione dello standard che supporta velocità di 400 Gbps è in fase avanzata di sviluppo. Se nel 2011 i dispositivi cablati, in base ai risultati di un'indagine condotta fa Cisco, erano responsabili del 55% circa del traffico IP, il traffico dati che viaggia attraverso connessioni wireless raggiungerà gli 11,2 exabyte nel corso del 2017. La velocità della rete resta il maggior ostacolo alla crescita anche se altri elementi, come ad esempio la riduzione dei consumi, hanno un impatto sempre più rilevante, complice l'aumentata sensibilità alle problematiche ambientali e la maggiore attenzione al risparmio energetico. In molti settori industriali i produttori di apparecchiature stanno considerando l'opportunità di utilizzare gli Fpga per soddisfare la richiesta di velocità sempre più elevate. Le prestazioni di un sistema sono determinate in larga misura dal "data throughput" (velocità effettiva di trasferimento dati) e per molti dispositivi, come ad esempio gli Fpga, la tecnica più comunemente adottata per incrementare il throughput prevede la realizzazione di bus on chip sempre più ampi. Negli Fpga non è raro utilizzare bus di ampiezza pari a 512 o 1.024 bit (o ancora più ampi) anche se un approccio di questo tipo comporta un incremento dell'utilizzo delle risorse disponibili e della dissipazione di potenza, oltre a introdurre un certo grado di complessità durante l'esecuzione di operazioni di confronto ad alta velocità o di checksum (somma di controllo) per ogni bit del bus. Anche se la progressiva riduzione delle geometrie di processo comporta un incremento delle prestazioni, il ritardo imputabile alle interconnessioni ha iniziato ad assumere un ruolo predominante nella determinazione del ritardo complessivo di un Fpga. Nonostante l’utilizzo di un processo migliore, è necessario apportare modifiche a livello architetturale al fine di affrontare in modo efficace il problema delle interconnessioni.

Un'architettura di nuova concezione

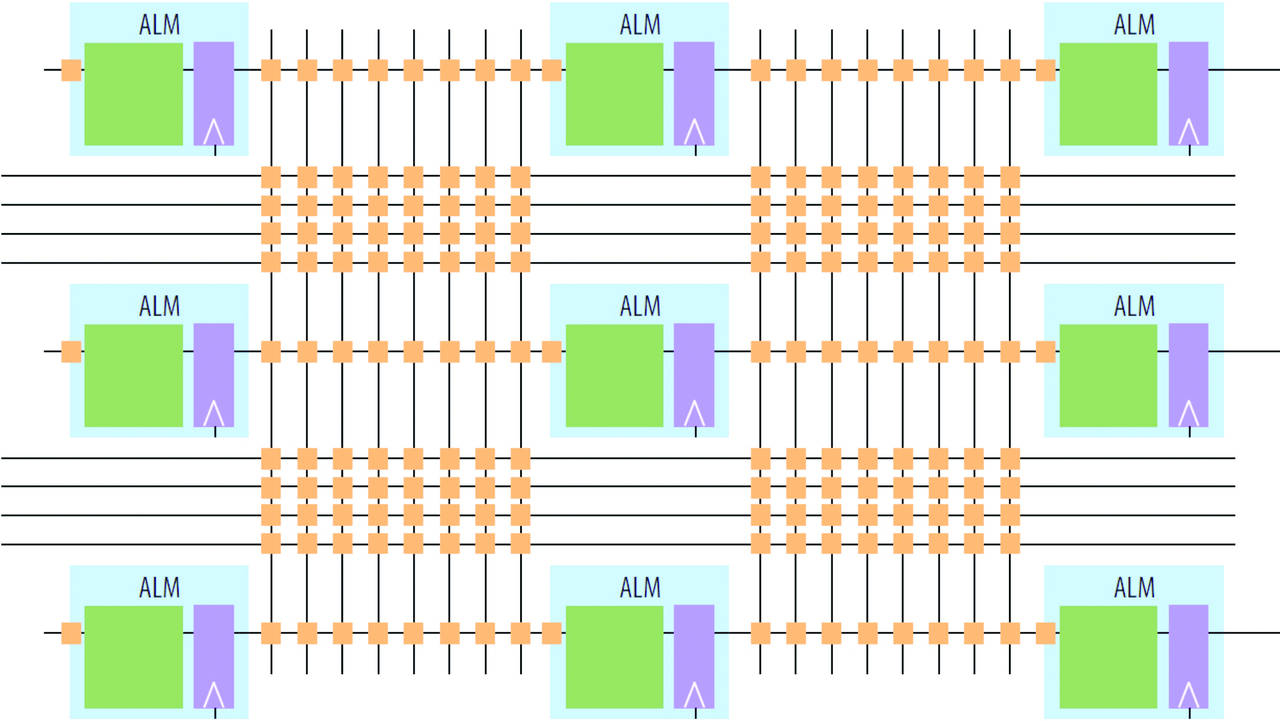

Un esempio di architettura che utilizza un approccio innovativo per risolvere il problema delle interconnessioni è l'architettura HyperFlex adottata da Altera per la realizzazione degli Fpga della linea Stratix 10. Basata sul processo Tri-Gate da 14 nm di Intel, questa architettura sfrutta il concetto di “registers everywhere” che prevede l’aggiunta di Hyper-Register bypassabili a ciascun segmento di routing nel core dell’Fpga e agli ingressi dei vari blocchi funzionali. Consideriamo lo schema di un Hyper-Register bypassabile dove il segnale di routing può oltrepassare il registro e andare direttamente verso il multiplexer oppure passare prima attraverso il registro. Come si evince dalla stessa figura il multiplexer è controllato da 1 bit della memoria di configurazione dell’Fpga. Nell'immagine in apertura è riportata una sezione di ridotte dimensioni della struttura dell’Fpga con 9 moduli Alm (Adaptive logic module) e l’istradamento delle interconnessione che li collega. L’ubicazione degli Hyper-Register è indicata dai quadrati posti all’intersezione di ciascun segmento di routing orizzontale e verticale. Al fine di ottimizzare le prestazioni di un progetto che utilizza questa architettura, gli utilizzatori dovrebbero adottare un processo che si articola su tre fasi: retiming dei registri, pipelining (inserimento di registri) e ottimizzazione del progetto stesso. Gli Hyper-Register consentono l’uso di tecniche di progettazione note e collaudate grazie alle quali è possibile incrementare sensibilmente le prestazioni del progetto rispetto a quelle ottenibili utilizzando le architetture Fpga tradizionali. Poiché vengono utilizzati gli Hyper-Register al posto dei registri tradizionali, le tre tecniche sono state rinominate di conseguenza: Hyper-Retiming, Hyper-Pipelining e Hyper-Optimization. L'operazione di retiming del progetto effettuata utilizzando gli Hyper-Register nell'istradamento delle interconnessioni non risulta affatto onerosa per lo sviluppatore e permette di ottenere un miglioramento medio delle prestazioni di un fattore pari a 1,4. Il risultato è stato ottenuto confrontando le prestazioni dei dispositivi della linea Stratix 10 con quelle conseguite con gli Fpga ad alte prestazioni della precedente generazione. Per eliminare i percorsi critici, l’Hyper-Retiming sposta i registri dei blocchi Alm e li posiziona nell’interconnessione in modo tale da bilanciare i ritardi tra i registri e consentire il funzionamento del progetto a una frequenza di clock più elevata. A causa della presenza di Hyper-register lungo tutta l’interconnessione, è senza dubbio possibile effettuare una scelta "a grana fine" per il posizionamento dei registri. Il retiming di tipo tradizionale richiede risorse di routing e logiche dell’Fpga aggiuntive per cui è necessario rieseguire le operazioni di compilazione, fitting (adattamento) e routing. Per contro l'Hyper-Retiming non richiede nessuna risorsa addizionale dell'Fpga e viene eseguito dopo l'operazione di "place&route", garantendo un sensibile aumento delle prestazioni senza praticamente nessun onere progettuale aggiuntivo. Nel caso dell’ Hyper-Pipelining, il progetto è sottoposto a operazioni di retiming e pipelining (ovvero inserimento di registri) utilizzando gli Hyper-Register. Questa tecnica non è particolarmente onerosa e garantisce un aumento medio delle prestazioni di un fattore pari a 1,6 nel caso dei dispositivi della linea Statix 10 (sempre rispetto agli Fpga ad alte prestazioni della generazione precedente). L’Hyper-Pipelining elimina i lunghi ritardi di routing mediante l’aggiunta di stadi di pipeline tra i blocchi Alm, consentendo quindi al progetto di operare a una frequenza di clock più elevata. Ancora una volta, gli Hyper-Register disponibili lungo l’interconnessione consentono una selezione di tipo "a grana fine" dell’ubicazione dei registri. Come nel caso dell’ Hyper-Retiming, l’Hyper-Pipelining non richiede risorse di routing e logiche dell’Fpga aggiuntive e viene effettuato una volta completata la fase di place-and-route. Una volta accelerati i percorsi dati mediante le operazioni di Hyper-Retiming e Hyper-Pipelining, alcuni progetti sono "limitati" dalla logica di controllo, come ad esempio lunghi anelli di retroazione e macchine a stati. Per conseguire maggiori prestazioni è necessario eseguire una “riorganizzazione” di queste sezioni logiche utilizzando percorsi di pre-elaborazione o di tipo feed-forward (diretti, quindi senza retroazione) equivalenti dal punto di vista funzionale al posto di lunghi percorsi di retroazione di natura combinatoria. In funzione del tipo di progetto preso in considerazione, l’operazione di Hyper-Optimization richiede uno sforzo leggermente superiore: in ogni caso è possibile ottenere un incremento in termini di prestazioni di un fattore pari a 2 (o anche superiore) con i dispositivi della serie Stratix 10 (sempre rispetto agli Fpga ad alte prestazioni della generazione precedente). Nelle architetture di tipo tradizionale questo processo va sotto il nome di ottimizzazione del progetto. Nel caso dell’architettura HyperFlex, questo processo è chiamato Hyper-Optimization poichè gli Hyper-Register "trasferiscono" i vantaggi propri delle tecniche di Hyper-Retiming e Hyper-Pipelining ai percorsi di tipo feed-forward o di pre-elaborazione. Al fine di sfruttare appieno i vantaggi derivati dal miglioramento delle prestazioni ottenibili con l’architettura Hyper-Flex e gli Hyper-Register è indispensabile far ricorso a una tool chain ottimizzata. Per questo motivo Altera ha sviluppato un nuovo set di tool che sono integrati nel software di progettazione Quartus II della società. Il software Hyper-Aware permette ai progettisti di sistemi di sfruttare appieno i vantaggi dell’architettura HyperFlex nonché ottimizzare la produttività degli sviluppatori.

Ottimizzazione delle prestazioni

Questo nuovo tool guida gli utilizzatori attraverso l’intero processo di ottimizzazione delle prestazioni identificando le sezioni del progetto che limitano le prestazioni, verificando il numero e l'ubicazione delle pipeline da utilizzare per incrementare le prestazioni e sottolineando i “colli di bottiglia” dei percorsi di controllo critici (come ad esempio lunghi anelli di retroazione). Questo tool “Fast Forward Compile” consente inoltre ai progettisti di prevedere in modo più accurato le prestazioni del loro progetto rispetto a quando possibile con i dispositivi della generazione precedente. Il tool Hyper-Retimer viene utilizzato verso la fine della compilazione del progetto. Esso esegue l’ottimizzazione delle prestazioni successivamente all’operazione di “place&route” utilizzando gli Hyper-Register per un Hyper-Retiming "a grana fine" ottimizzato. L'Hyper-Retimer consente inoltre di effettuare l’Hyper-Pipelining in maniera molto più semplice rispetto a un’operazione di pipelining tradizionale. Il report ottenuto dal Fast Forward Compile identifica quali sono i domini di clock che possono trarre vantaggio dagli stadi della pipeline e il numero di stadi di pipeline richiesto. Una volta che il progettista ha modificato la descrizione Rtl e piazzato il numero stabilito di stadi di pipeline al confine di ogni dominio di clock, l’Hyper-Retimer posiziona automaticamente i registri all’interno del dominio di clock nella posizione più idonea per ottimizzare le prestazioni. Questo piazzamento automatico, unitamente alle informazioni desunte dal Fast Forward Compile, semplifica enormemente l’operazione di pipelining. La combinazione tra una nuova architettura Fpga e il processo Tri-gate da 14 nm permette di ottenere significativi miglioramenti, in termini di prestazioni e di consumi, rispetto ai dispositivi della generazione precedente. Queste migliorie costituiscono un valido ausilio per gli sviluppatori che devono realizzare prodotti in grado di tenere il passo con l’evoluzione tecnologica in atto.