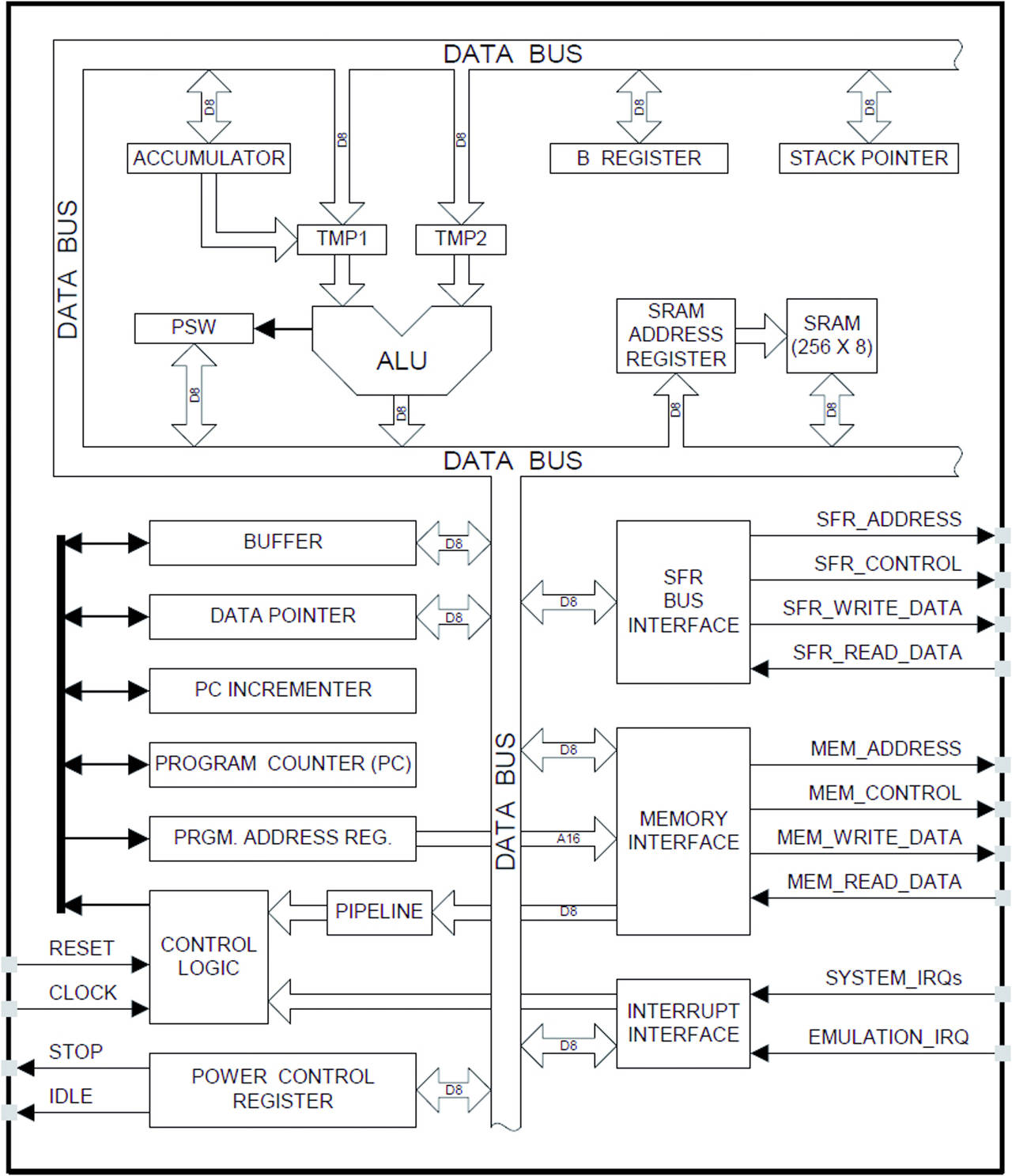

Il supercollaudato core 8051 conobbe una seconda giovinezza quando, nel 1998, giunse a scadenza il brevetto della sua architettura. Da quel momento, il mercato fu invaso da una moltitudine di nuove Mcu 8051; alcune di esse del tutto conformi all'originale, altre, invece, con modifiche a vari livelli. Tra queste ultime, l'architettura Silicon Labs 8051 è riconosciuta essere una delle più prestanti: pur mantenendo la compatibilità di codice con la capostipite, è stata modernizzata e “Risc-izzata”, ottenendo un massiccio incremento di prestazioni. Il core originale Intel 8051 si prendeva 12 cicli per eseguire una singola istruzione, il che significa che a 12 MHz, ad esempio, era in grado di eseguire un milione di istruzioni al secondo. Al contrario, un nuovo core Silicon Labs 8051 da 100 MHz lavora a 100 Mips, vale a dire ben 100 volte più veloce dell'originale, con una frequenza di clock solo circa 8 volte più alta. Silicon Labs ha implementato la sua versione del core 8051 in architettura Von Neuman con pipeline a tre stadi. La semplicità di questa tecnologia, unita alla logica di decodifica immediata delle istruzioni di una macchina a 8 bit, consente a questo dispositivo realizzato in processo 0.35-micron di operare a 100 MHz. Per garantire facilità di context switching, visto che la compatibilità di codice con l'8051 classico era un punto irrinunciabile, è stato mantenuto un register file da 32 byte a quattro settori. Per le stesse ragioni, sono stati preservati anche tutti gli altri elementi hardware della versione classica.

Innovazioni e vantaggi

Per sfruttare al meglio le capacità dei nuovi 8051, è stato necessario creare una definizione di sistema che potesse riconoscere e valorizzare le prerogative offerte da questa architettura. Ad esempio, il core 8051 concretizza la possibilità di eseguire operazioni logiche direttamente su alcuni registri e locazioni di memoria: funzione, questa, molto apprezzabile nella maggior parte delle applicazioni di controllo, in ambito industriale o no. Data la frequenza di lavoro dei dispositivi Silicon Labs a 8 bit, queste operazioni possono essere effettuate in un singolo ciclo. Questo particolare approccio permette di migliorare il tempo di risposta del controllo, il che significa che una definizione di bit-banged bus può operare a una velocità abbastanza ragionevole se paragonata alla corrispondente implementazione hardware. Ad esempio, una Spi full-duplex bit-banged può essere implementata in 12 periodi di clock per bit, il che equivale a reggere un bit rate maggiore di 8 MHz con un clock di 100 MHz. Un’altra miglioria dell'8051 è stata ottenuta implementando il controllore in un processo da memoria flash e dotarlo di una flash embedded, cosa che rende più veloce la partenza e l'esecuzione del codice. Naturalmente anche il percorso di fetch delle istruzioni deve essere al passo con i requisiti di velocità, così sono state implementate ulteriori aggiunte, quali pre-fetch buffer e cache, nonchè branch-target-buffer. Le ultime Mcu a 8 bit di Silicon Labs, come l'EFM8UBx, continuano la tradizione di implementare un pre-fetch buffer da 16 bit allo scopo di rendere possibile l'operatività a 50 MHz. Date le caratteristiche prestazionali di questi sistemi, si è reso inoltre necessario implementare una nuova architettura di I/O in grado di supportare un considerevole numero di periferiche operanti simultaneamente o in condivisione. A questo scopo, è stata sviluppata una architettura priority crossbar al fine di permettere a tutte le periferiche di accedere a quasi tutte le porte in maniera deterministica. In tal modo, si è ottenuta la possibilità di gestire molte periferiche ad alta velocità all’interno dello stesso sistema con un gran numero di I/O, tutti sotto il controllo della Cpu ad alte prestazioni. Il fatto che il core 8051 sia una macchina a 8 bit implica che lo spazio di registri sia limitato a 256, cosa assolutamente insufficiente in una Cpu ad alte prestazioni che deve gestire molte periferiche. Il problema è stato risolto implementando un concetto tipo pagina di memoria in cui sono stati definiti tanti spazi di indirizzi da 256 byte e un meccanismo per saltare da uno all'altro. Alcuni - se non la maggior parte - dei registri di sistema, come pure registri di periferiche essenziali, sono stati resi disponibili su ogni pagina. Altra eredità del core originale 8051 è il suo tempo di reazione agli interrupt. Proprio per la natura della sua latenza di esecuzione di 12 cicli, la latenza di interrupt potrebbe arrivare addirittura a centinaia di cicli, rallentando così la capacità di controllo. I dispositivi con più alte prestazioni hanno ovviamente una latenza di interrupt decisamente migliore, per rendere più veloce la risposta del sistema nei confronti degli interrupt di controllo o di quelli provenienti da sensori. A tale scopo, alcune delle più recenti Mcu 8051 di Silicon Labs sono state dotate di una gerarchia di interrupt con quattro livelli di priorità, cosa che permette una maggior risoluzione nella gestione degli interrupt, essenziale in un sistema caratterizzato da un numero elevato di periferiche.

Data la natura delle più recenti memorie di sistema, gli accessi sono stati concepiti intrinsecamente a due cicli. In questo modo, tutti gli accessi alla memoria si possono seguire vicendevolmente, senza soffrire di alcun ritardo della pipeline. È stata pure mantenuta la possibilità di effettuare operazioni logiche sulle locazioni di memoria: anche queste a 2 cicli, dal momento che avvengono come operazioni read-modify-write. Nonostante la considerevole velocità di clock, le Mcu 8051 ad alte prestazioni non sono state progettate per eseguire rapidamente operazioni aritmetiche complesse. Ad esempio, una Mcu 8051 Silicon Labs ha bisogno di 143 cicli per eseguire moltiplicazioni a 16 bit. Alcune Mcu 8051 Silicon Labs ad alta velocità implementano un Mac a 16 bit con accumulatore da 40 bit, una tecnica che permette di eseguire operazioni Mac da 16 bit a singolo ciclo o moltiplicazioni. Certamente questo comporta alcuni cicli per caricare e scaricare i dati, ma grazie alla struttura a pipeline del Mac, questi possono essere trasferiti nei registri di ingresso mentre il Mac sta elaborando i dati precedenti.

Le migliori prestazioni del core 8051 hanno inoltre reso più efficienti alcuni elementi della dotazione di periferiche, tra cui Usb a bassa o alta velocità. Una Mcu 8051 Silicon Labs che lavora a 50 MHz ha infatti abbastanza potenza per gestire uno stack Usb mantenendo comunque l'operatività di tutte le periferiche a pieno regime: un tale livello di prestazioni consente anche un ragionevole tempo di risposta nel pilotare 2 Adc da 1MSample come pure il solito mix di Uart, Spi e Dac. Le precedenti versioni di Mcu 8051 non erano, nella maggior parte dei casi, in grado di supportare le funzioni di emulazione di circuiti in-system per il debug, mentre per il core 8051 di Silicon Labs tale supporto è stato previsto fin dall'inizio. Per questo è stata sviluppata C2, un’interfaccia di debug a 2 fili ultra-piccola ma potente, presente sulla maggior parte delle Mcu 8051 di Silicon Labs.

Alcuni 8051 ad alto numero di pin implementano un'interfaccia di memoria esterna capace di dialogare con qualsiasi dispositivo memory-mapped come, ad esempio, Ram o altri controllori. In alcune applicazioni è inoltre possibile gestire un controller Ethernet tramite una Mcu 8051 Silicon Labs a 50 MHz, con spazio sufficiente a far girare anche altre periferiche.

Il portfolio Silicon Labs a 8 bit comprende anche Mcu wireless basate su core 8051 abbinato a un transceiver a bassa potenza e frequenza sotto il GHz. La Cpu utilizzata in questi casi è abbastanza potente da far funzionare un intero stack radio, avanzando anche alcuni Mips per elaborare i dati prima della loro emissione. Queste Mcu wireless di piccole dimensioni e bassissima potenza si caratterizzano per il consumo energetico estremamente ridotto in sleep mode, pur conservando tutti gli stati: sono quindi la soluzione ideale per nodi di sensori wireless in cui il basso consumo è una caratteristica irrinunciabile.

Nello stesso portfolio a 8 bit di Silicon Labs si trovano anche microcontrollori omologati per applicazioni automotive, provvisti di oscillatore con precisione 0,5% e interfaccia Can: una combinazione vantaggiosa che permette di eliminare il quarzo dall'elenco componenti a tutto vantaggio di produzione e affidabilità. In aggiunta, questa implementazione senza quarzo offre la possibilità di sintonizzare l'oscillatore a step di 30 ps, consentendo di realizzare sofisticati controlli Pwm con un posizionamento estremamente accurato dei fronti. Questa tecnica è possibile solo grazie alla velocità del core che permette un controllo software di tale funzione. Un altro vantaggio che il core 8051 presenta rispetto a molti dei suoi concorrenti a 32 bit è la possibilità di accedere agli I/O alla velocità del bus. Ad esempio, se c'è la necessità di testare un pin e in funzione del suo valore si deve decidere di cambiarne lo stato, una Mcu 8051 Silicon Labs a 100MHz è in grado di eseguire questa operazione in 50 ns. Un processore a 32 bit che lavora a 100MHz avrà i suoi Gpio sull'APB bus. Ciò significa che girerà ad una frequenza più bassa della velocità del bus (possibilmente la metà), tanto che un processore che lavora a 100 MHz potrà accedere ai suoi Gpio solo a 50 MHz e sarà in grado di prendere decisioni a tale velocità. Così una Mcu a 32 bit impiegherà circa 140 ns ad eseguire la lettura di un pin, un confronto, una istruzione di cambio di configurazione della porta e una istruzione di scrittura. Facendo un paragone, un 8051 che funziona a 100 MHz sarà in grado di eseguire questa operazione in circa 50 ns. Naturalmente, se l'8051 funzionasse a 50 MHz, il tempo per cambiare la configurazione della porta diventerebbe 100 ns. Nelle Mcu 8051, grazie alla maggior semplicità della gerarchia di bus, i branch possono essere elaborati più velocemente che su una macchina a 32 bit con gerarchia di bus. Questa possibilità è innata nella architettura 8051 ed è disponibile in tutti i prodotti basati su 8051 di Silicon Labs, compresa la nuova famiglia EFM8.

Le Mcu 8051 nell'era IoT

L'ormai collaudato core 8051 è stato significativamente modernizzato nel corso degli anni e oggi può vantare una grandissima quantità di installazioni con milioni di righe di codice scritte appositamente. Da questa enorme libreria i progettisti possono attingere per sviluppare le loro applicazioni a 8 bit basate su questo core. Le recenti applicazioni di Internet of Things come, ad esempio, le apparecchiature connesse e le reti di sensori, possono interamente avvalersi delle prestazioni delle Mcu 8051. Queste applicazioni IoT sono solitamente ricche di sensori e controllori e devono far fronte a severi vincoli in termini di consumi energetici, ingombri e costi. Il set di istruzioni 8051, ormai universalmente adottato e testato nel tempo, continua a essere la scelta giusta per molte applicazioni che richiedono un equo bilanciamento tra efficienza e rapporto prezzo/prestazioni. Bisogna quindi riconoscere che anche nel caso della pluriennale popolarità del core 8051, vale il vecchio detto "più le cose cambiano, e più rimangono le stesse".