I sistemi embedded stanno assistendo a una rapida crescita sia nei mercati esistenti che in quelli in via di sviluppo, e gli analisti prevedono che il fatturato globale di tali sistemi varrà 225 miliardi di euro entro il 2021. Questa crescita è trainata dal continuo sviluppo di diverse importanti mega-tendenze, incluso l’Internet delle Cose e l’Internet delle Cose Industriale, l’Industria 4.0 e i sistemi cyber-fisici, oltre alla proliferazione dei sistemi di visione embedded ai bordi del sistema. Molte di queste applicazioni richiedono lo sviluppo e la realizzazione di sistemi ad alte prestazioni ai bordi del sistema. Per applicazioni caratterizzate da un grande numero di installazioni, i costi di ingegnerizzazione ricorrenti sono di importanza critica e determineranno la fattibilità della soluzione. Un fattore trainante per la riduzione dei costi d’ingegnerizzazione ricorrenti è la realizzazione di un sistema d’integrazione più stretta, che comprende l’integrazione dei componenti. Un tipico sistema embedded contiene componenti fra cui processori, logica digitale, interfacce, memorie volatili e non volatili, componenti a segnale misto, sensori ed elementi di supporto come temporizzatori e alimentatori. Un’integrazione più stretta consente anche di ridurre la complessità e di contenere i costi della scheda a circuito stampato e del suo assemblaggio.

Ottimizzati in base ai requisiti applicativi

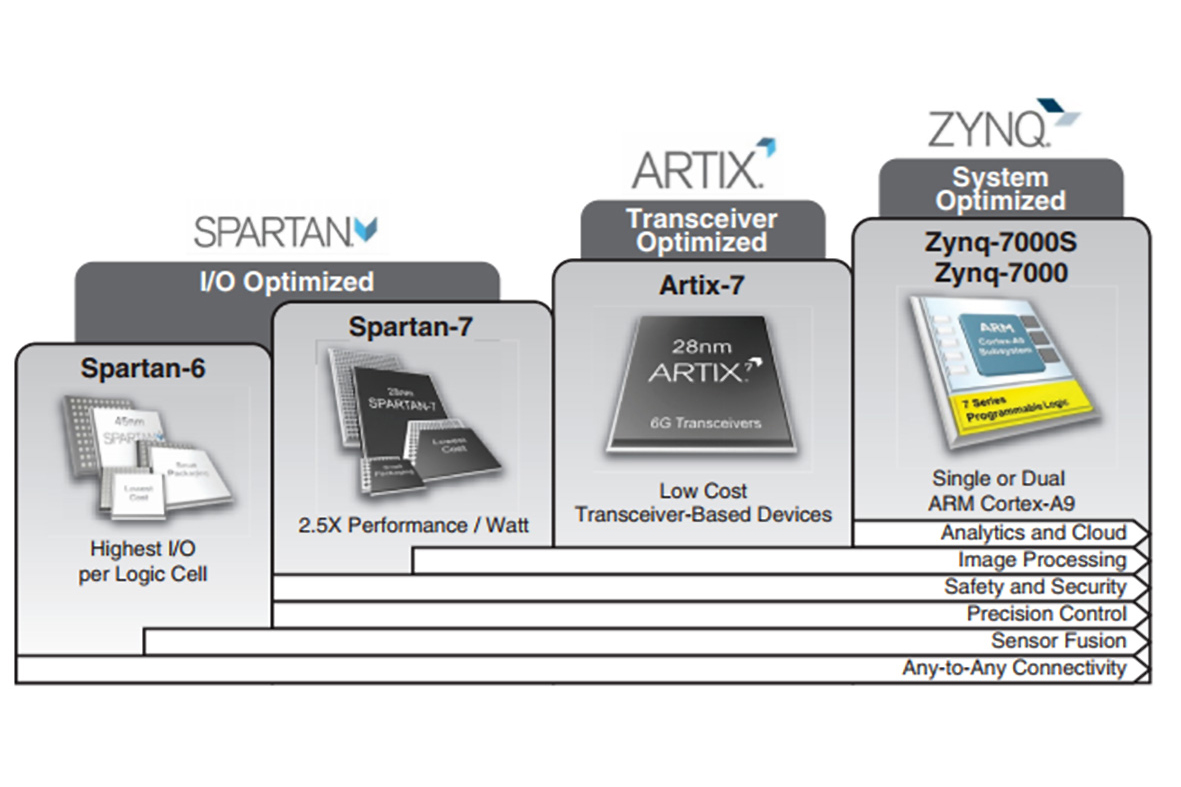

I dispositivi Interamente Programmabili come gli Fpga e i System-on-Chip eterogenei del portafoglio di prodotti ottimizzati nei costi di Xilinx non solo forniscono le prestazioni richieste, ma assicurano anche l’ottenimento di un’integrazione più stretta. Questi dispositivi sono realizzati su misura per diversi requisiti delle applicazioni:

- ottimizzazione degli I/O - fornita dalle famiglie Spartan-6 e Spartan-7;

- ottimizzazione del transceiver - fornita dalla famiglia Artix che offre gigabit transceiver;

- ottimizzazione a livello di sistema - fornita dalle famiglie di SoC Zynq-7000 con core Cortex-A9.

Il portafoglio prodotto serve applicazioni che vanno dal Cloud computing e dall’elaborazione delle immagini alla fusione dei sensori, al controllo di precisione e alla sicurezza e protezione. Usando questa gamma di dispositivi, è possibile creare un sistema più strettamente integrato grazie alla possibilità di effettuare:

- Integrazione del processore - È possibile combinando il processore e la logica digitale all’interno dello stesso dispositivo. Questo può essere ottenuto usando il core sintetizzabile MicroBlaze a 32 bit o i core Cortex-A9 del dispositivo Zynq-7000.

- Integrazione a segnale misto - È possibile sfruttando le risorse analogiche all’interno dei dispositivi di serie 7. Il modulo a segnale misto Xadc fornisce due Adc da 1Msps in grado di multiplare internamente fra 17 ingressi differenziali. Per fornire funzionalità Dac, si può ricorrere alla modulazione ad ampiezza di impulso, mentre per velocità di campionamento più alte è possibile implementare tecniche di tipo delta sigma, sfruttando le risorse differenziali delle celle IO.

- Semplificazione delle interfacce - La logica programmabile offre la possibilità di realizzare interfacce universali, grazie all’ampia gamma di standard supportati direttamente dalle strutture IO. Abbinata alla capacità di eseguire funzioni di protocollo all’interno della logica programmabile, questa funzionalità consente di implementare con semplicità interfacce proprietarie, su misura e standard. Questa flessibilità consente inoltre di ridurre il numero di dispositivi richiesti per lo strato fisico, come ad esempio i dispositivi Hdmi o Mipi Dphy.

- Semplificazione dell’architettura di memoria - Usando un approccio unificato, è possibile memorizzare il software applicativo e il flusso di bit dell’Fpga all’interno della stessa memoria non volatile. Le memorie volatili come le Ddr possono inoltre essere condivise fra il processore e l’applicazione Fpga.

- Semplificazione dell’architettura di temporizzazione - L’integrazione all’interno di un singolo dispositivo elimina la necessità di avere oscillatori separati per la logica digitale e per i processori, mentre le unità di gestione della temporizzazione, e la disponibilità di Pll, Anelli ad Aggancio di Fase e i dispositivi a segnale misto per la gestione del clock, possono essere usati per generare ulteriori segnali di clock del sistema, e per fornire la capacità di regolare rapidamente la frequenza e la fase in uscita.

Lo sviluppo di queste applicazioni integrate può anche fare affidamento su un’ampia gamma di core IP forniti all’interno della libreria Vivado. Inoltre, per applicazioni algoritmiche e di elaborazione dei segnali/delle immagini, è possibile ricorrere alla sintesi ad alto livello per definire le funzionalità, usando un linguaggio ad alto livello come il C o il C++, e riducendo il tempo complessivo di sviluppo.

Un esempio di integrazione

I sistemi IIoT e cyber-fisici contengono spesso sistemi di visione embedded, sistemi di controllo di motori o attuatori, e interconnettività su cavo e wireless, oltre a sensori di posizione e sensori ambientali. Una soluzione tradizionale non integrata farebbe uso di un processore per eseguire l’interfacciamento dei sensori, la sequenza di elaborazione e il conseguente controllo del motore o dell’attuatore. Questa soluzione, oltre a presentare un numero superiore di componenti, introduce anche temporizzazioni più complicate e un’architettura di alimentazione più complessa, che contribuiscono a far aumentare i costi di ingegnerizzazione ricorrenti. Una soluzione integrata ottimizzata nei costi può essere implementata usando un dispositivo Spartan-7, Artix-7 o Zynq-7000, in relazione ai requisiti di elaborazione e di prestazioni. Se si sceglie uno Spartan-7 o un Artix-7, la soluzione integrata è costituita dall’implementazione di un processore MicroBlaze all’interno dell’Fpga. Le istanziazioni di MicroBlaze sono personalizzabili con una gamma di prestazioni disponibili per l’applicazione in questione. Tuttavia, quando è implementato per fornire le massime prestazioni, il core MicroBlaze è in grado di fornire rispettivamente 262 Dmips a 181 MHz o 228 Dmips a 157 MHz all’interno di un dispositivo Artix-7 o Spartan-7. Usando il generatore di interfacce di memoria, il core MicroBlaze e la logica sono in grado di interfacciarsi con la memoria volatile Ddr, mentre è possibile usare una memoria Flash con interfaccia Qspi o con interfaccia tradizionale parallela, per archiviare non solo il flusso di bit dell’Fpga, ma anche il software applicativo. Il blocco Xadc interno può essere usato per l’interfacciamento con i sensori ambientali, e il suo multiplatore interno fornisce la capacità di effettuare cicli fra i sensori in ingresso. Dato che lo Xadc include due convertitori Adc, è possibile convertire gli ingressi simultaneamente, migliorando la capacità del sensore. È possibile implementare un ricevitore per supportare uno strato fisico DPhy Mipi con velocità di trasmissione dati fino a 800 Mb/s, usando celle IO aggiuntive e una rete di resistori esterni. Questo consente di decodificare i dati dei sensori di immagini usando il core IP relativo al sottosistema ricevitore Csi-2, e di elaborarli usando l’unità di elaborazione delle immagini. Quest’ultima si può avvalere della potenza della sintesi ad alto livello effettuata attraverso Vivado Hls e può fare uso delle librerie xfOpenCV disponibili come parte dello stack di accelerazione reVision. Se è richiesta una soluzione a maggiore intensità di calcolo, si può usare un dispositivo Zynq a core singolo o dual core, che fornisce fino a 2500 Dmips a 1 GHZ. Il dispositivo SoC Zynq consente inoltre di ottenere una maggiore integrazione a livello di sistema, con il supporto per una gamma di interfacce standard ad alte prestazioni come GigE, Usb2 o PCIe, unitamente ad interfacce embedded di sistema di uso comune come Uart, Can, Spi o I2C. Gli stessi tool di sviluppo possono essere usati sia per la soluzione basata su SoC, sia per quella basata su Fpga. La stretta integrazione fra il sistema di elaborazione e la logica programmabile all’interno dello Zynq, abbinata all’uso degli stack di accelerazione come reVision, consentono l’accelerazione di OpenCV e le applicazioni di apprendimento automatico con relativa semplicità.