Per soddisfare gli ultimi standard green per gli alimentatori di qualsiasi settore industriale, comprese le applicazioni automotive e consumer, è necessario progettare pensando a un incremento di efficienza ed affidabiltà. Un ruolo chiave in questo lo gioca il Climate Savers Computing Initiative, un partner del programma Energy Star e parte di un’iniziativa per incoraggiare i produttori a migliorare l'efficienza di erogazione della potenza dei computer, riducendo il consumo di energia quando lo stesso è in uno stato di attesa o di riposo. Csci classifica i prodotti in bronzo, argento, oro e, da ora, come più recente specifica, anche platino. È possibile realizzare un alimentatore da 720 W Ac-Dc completamente controllato digitalmente che soddisfi tutte le specifiche Csci platinum, oltre a fornire funzioni e caratteristiche application-specific. Le specifiche platinum si applicano ad alimentatori con ingresso Ac singola-fase con una gamma di potenze comprese tra 500 W e 1 kW, misurati su un ingresso a 230 Vac. Queste definiscono anche il fattore di potenza in funzione del carico.

Le topologie interallacciate

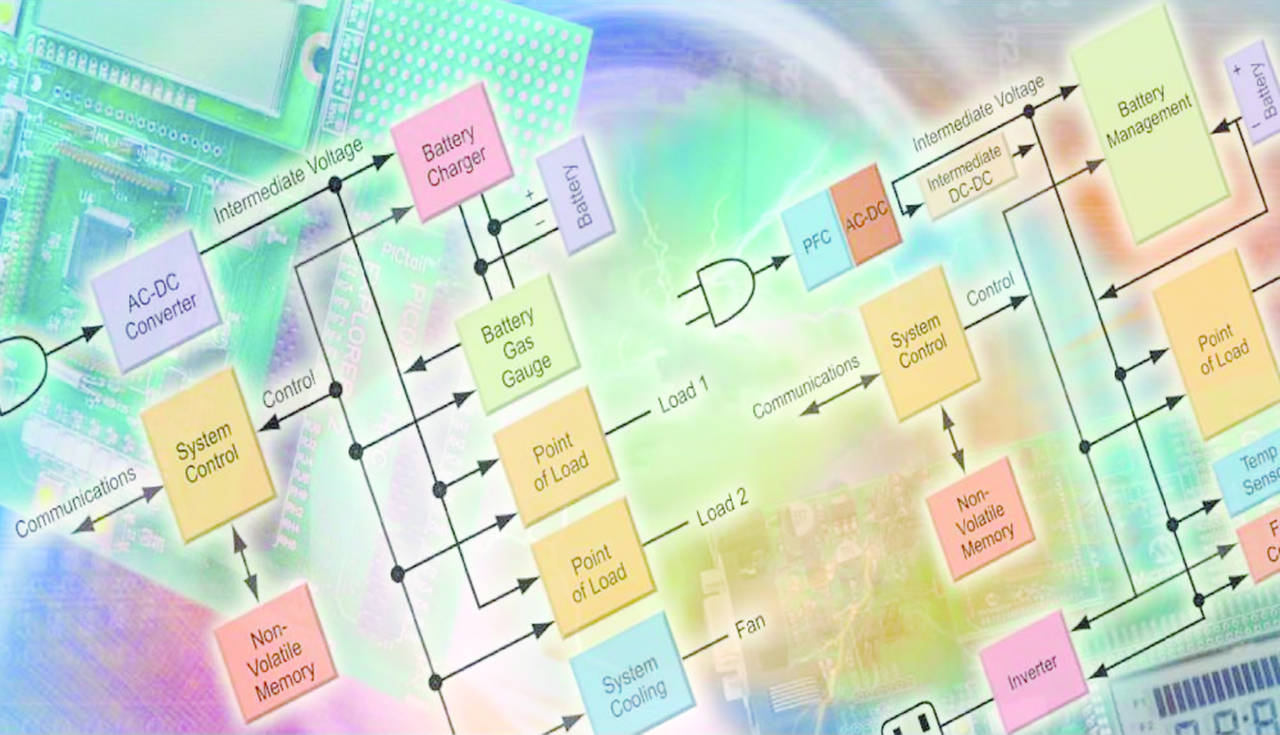

Le topologie interallacciate offrono evidenti vantaggi quando siano richiesti elevata efficienza, affidabilità e alta densità di potenza. Sdoppiando ogni topologia in due fasi parallele e interallacciando il loro funzionamento con uno sfasamento di 180˚ si riduce la corrente ripple. I ridotti valori di corrente picco-picco in topolgie interallacciate si traducono in temperature di funzionamento inferiori, il che equivale una riduzione delle perdite. Poiché ogni fase ha necessità di trasportare solo metà della corrente complessiva, le perdite di conduzione nei condensatori, nel rame del Pcb e magneti vengono ridotte di quattro volte. Ciò accade perché la corrente appare come un valore quadratico nell’equazione di calcolo delle perdite. Un altro vantaggio delle topologie interallacciate è la dimezzata corrente rilevata per ogni fase, che si traduce in un minore ingombro di bobine e trasformatori, e dimensioni ridotte anche delle tracce del Pcb, Mosfet, dissipatori di calore e diodi. In questo schema di riferimento, sia lo stadio amplificatore di Pfc (Power factor correction) che il two-switch forward converter sono stati progettati in una architettura two-phase interleaved. I primi componenti, posti sui terminali di alimentazione, sono un filtro e un condensatore da 1 μF, attraverso i terminali, per la soppressione Emi. La bobina viene seguita da due fusibili, uno sulla linea, l’altro sul neutro. Un varistore da 470 V attraverso i terminali di alimentazione aggiunge protezione verso i picchi di tensione transienti. Lo stadio filtro di ingresso utilizza due ulteriori filtri costituiti da una bobina in common mode, due condensatori Y collegati alla messa a terra, e un condensatore a film di polipropilene metallizzato antidisturbi (condensatore X) collegato attraverso linea e neutro. Un Ntc (Negative temperature coefficient), con una zero power resistance di 10Ω a 25˚C, viene utilizzato per limitare la corrente di spunto sotto i 40 A (20 A tipico). Questo Ntc sarà bypassato da un relay non appena la tensione grezza sia stata stabilizzata e i controller iniziano a risalire il sistema. La tensione di ingresso è collegata al rettificatore a ponte con un limite di funzionamento di 1,3kV e 43A. Attraverso l’uscita di questo rettificatore a ponte, un altro varistore ed un condensatore di soppressione delle interferenze sono stati posizionati a protezione dai transienti. Il converter interlacciato Pfc, utilizza due boost converter identici accoppiati in parallelo e sfasati di 180˚ l’uno rispetto all’altro. Lo stadio Ipfc è un converter Ac-Dc, che converte la tensione Ac di alimentazione in ingresso in un output Dc ad alta tensione regolata. Lo stadio Pfc modella anche la corrente dell'induttore in maniera simile alla tensione Ac raddrizzata per mantenere un elevato fattore di potenza e bassa distorsione armonica totale. Questo stadio opera in Ccm (Continuous conduction mode) per ridurre il contenuto di armoniche nella corrente di ingresso. La topologia di amplificazione Pfc richiede che solo un Mosfet low-side venga pilotato. Il driver per Mosfet 2-canali MCP14E4 di Microchip, con uscite Cmos push-pull con capacità sourcing e sinking di 3,5 A a 12 V, è stato selezionato per pilotare entrambe le fasi. Due current sense transformer con un rapporto di trasformazione 50:1 sono stati usati per il rilevamento di corrente. Questi sono stati posizionati sul lato drain dei Mosfet low-side anziché dal lato source per ottenere un miglior feeedback con un ridotto rumore di commutazione. L’uscita di corrente viene convertita in un segnale di tensione da un resistenza di carico da 15 Ω. Un gruppo di 4 resistenze serie-parallelo – con due resistenze da 15 Ω in serie e due resistenze da 15Ω in parallelo – è stato utilizzato per questo carico CT per ridurre le tolleranze relative dello shunt e ottenere una maggiore precisione. Le connessioni in serie sono anche utilizzate per dimezzare la tensione per gli ingressi di comparazione del digital signal controller dsPIC (DSC).

Il Mosfet è il transistor di potenza 600V CoolMOS C6 di Infineon. Il diodo IPfc scelto è lo Z-Rec rectifier (C3D20060D), un diodo Schottky al carburo di silicio di Cree. Questo diodo è stato scelto per la sua tensione inversa, per la corrente diretta, bassa caduta di corrente diretta, e velocità di switching. Le perdite di reverse recovery tipicamente costituiscono una significativa percentuale delle perdite di potenza dei boost converter. Queste perdite vengono ridotte utilizzando diodi al carburo di silicio, dato che questi hanno un tempo di reverse recovery associato praticamente nullo. Consideriamo la topologia di base con i suoi percorsi di corrente e tensioni negli schemi di two-switch forward converter interlacciato. A differenza della topologia dei flyback converter, i forward converter usano trasformatori di corrente per trasportare energia all’output durante il perido di funzionamento dei Mosfet. In un two-switch forward converter, vengono utilizzati Mosfet high-side e low-side per applicare tensione attraverso l’avvolgiento primario. Entrambi sono commutati su on e off simultaneamente. Non appena la tensione viene applicata attraverso l’avvolgimento primario, tutti gli avvolgimenti vanno su positivo. Quando il Mosfet Q3 viene commutato su on, la corrente sull’avvolgimento secondario si accumulerà. Poiché la corrente potrebbe ancora fluire attraverso L1 e C1, il carico e il percorso di ritorno attraverso D3, la corrente si accumulerà fino a che il suo valore raggiunga e superi quello della corrente attraverso D3. A questo punto, la corrente diretta attraverso D3 si fermerà e la tensione VS attraverso l’avvolgimento secondario verrà applicata all’inizio di L1. Una volta che ciò sia accaduto, la bobina L1 e il condensatore di uscita C1 verranno caricati e l’alimentazione trasportata all’output. Quando i Mosfet Q1 e Q2 sono commutati su off, le tensioni su tutti gli avvolgimenti verranno invertite. L’effetto flyback durante questo processo risulterebbe in elevati livelli di tensione attraverso l’avvolgimento primario del traspormatore. Questi picchi vengono bloccati dai diodi paralleli D1 e D2. Questi diodi alimentano l’energia immagazzinata nel campo magnetico nuovamente nelle linee di alimentazione. Poiché il processo di carica e scarica assorbono circa la stessa quantità di tempo, il duty ratio non deve essere superiore al 50%, dato che questo potrebbe tradursi in una saturazione di scala del nucleo del trasformatore. Quando la tensione sul lato secondario si inverte, il Mosfet Q3 è commutato su off e la bobina L1 continua a pilotare corrente in C1 ed il carico che fa si che D3 divenga forward-biased. In un’architettura interlacciata, le fasi A e B sono commutate con una sfasatura di 180˚. Dato che il massimo duty ratio è limitato al 50%, il tempo totale dirante il quale la corrente di uscita viene pilotata attraverso L1, C1 e D3 diviene molto piccolo. Sebbene un circuito di gate driver potrebbe anche essere progettato utilizzando un direct drive per il lowside ed un gate drive transformer addizionale per highside, questo potrebbe causare variazioni dei tempi tra entrambi gli switch, traducendosi in un decremento dell’efficienza ed elevato stress dei componenti. Pertanto, è più facile utilizzare un one gate drive transformer con un ugual numero di spire per l’avvolgimento secondario. Per ottenere feedback di elevata larghezza di banda, al fine di aumentare le prestazioni, per il feedback di corrente di uscita è stato utilizzato un resistore di shunt high side. Questa resistenza è stata posta tra il condensatore di uscita ed il filtro di uscita per rilevare step di carico il prima possibile. Per rodurre le perdite causate dalla resistenza di questo resistore di shunt, due resistenze da 500 μΩ sono state usate in parallelo. Un monitor di corrente high-side utilizzante l’op-amp MCP6H02 di Microchip forniva il feedback. Normalmente, i forward converter sono progettati con con un diodo rettificatore e un diodo free-wheeling. Tuttavia, in questo schema di riferimento il diodo rettificatore è stato sostituito da un Mosfet per aumentare l’efficienza e compensare i ritardi di segnale causati da perdite di induttanza nell’avvolgimento del trasformatore secondario.

Miglioramento delle prestazioni

Per migliorare l’efficienza, lo switching period dello stadio Pfc viene modificato quando il sistema funziona in steady state per ridurre le perdite di commutazione. La frequenza di commutazione è regolata dinamicamente, in base alle condizioni del carico di corrente. I diversi valori possibili di Pfc switching period sono archiviati in un lookup table. I valori sono selezionati dal lookup table in base alla corrente di riferimento calcolata per il loop di controllo della corrente. Un algoritmo software frequency jitter è stato implementato al fine di migliorare le prestazioni dei test Emi. I jitter algorithm ottengono questo ampliando il rumore Emi generato dal sistema attraverso una gamma di frequenze da una modulazione triangolare della frequenza di commutazione. La tensione grezza di output dello stadio Pfc è ridotta a steady state per migliorare l’efficienza nei piccoli carichi. Questo viene controllato direttamente dal lato secondario trasmettendo informazioni sulla corrente di carico di ritorno al lato primario.