In vista della miniaturizzazione dei nodi IoT e dei dispositivi indossabili spesso non è possibile evitare di espandere la memoria. Invece di ricorrere in modo predefinito a una struttura del bus del controller a 32 bit, i progettisti dovrebbero prendere in esame l'interfaccia HyperBus a doppia velocità dati (DDR) a 8 bit ad alta velocità, pari a 333 Mbps, sia per gli indirizzi, sia per i dati.

Per quanto i progettisti tentino di evitare le espansioni, queste si rendono spesso necessarie a causa dell'aumento dei requisiti di memoria durante lo sviluppo. In alternativa, gli sviluppatori creano semplicemente progetti a prova di futuro prevedendo le esigenze di espansione che sorgeranno in un momento successivo.

Per quanto i progettisti tentino di evitare le espansioni, queste si rendono spesso necessarie a causa dell'aumento dei requisiti di memoria durante lo sviluppo. In alternativa, gli sviluppatori creano semplicemente progetti a prova di futuro prevedendo le esigenze di espansione che sorgeranno in un momento successivo.

Con HyperBus, i microcontroller sono in grado di supportare memorie RAM e flash esterne sul medesimo bus, anziché dover ricorrere al bus a 16 bit dei dati e a quello a 16 bit degli indirizzi di una tipica interfaccia a 32 bit, e ai relativi pin di controllo. HyperBus funziona con tutti i dispositivi di memoria dotati della relativa porta, ed è un'interfaccia efficace e intuitiva per le espansioni di memoria a bassa piedinatura nelle applicazioni con vincoli di spazio.

Benché il funzionamento del bus sia trasparente al firmware, per garantire una progettazione robusta è importante che gli sviluppatori senza una conoscenza approfondita del protocollo HyperBus si familiarizzino con il funzionamento dei segnali di bus ad alta velocità. Questo articolo descrive anzitutto il funzionamento dell'interfaccia HyperBus. Presenta poi i microcontroller che incorporano l'interfaccia, mostrando agli utenti come applicarla in modo efficace e come collaudare i loro progetti.

L'interfaccia HyperBus

Come già ricordato, HyperBus utilizza un'interfaccia DDR ad alta velocità a 8 bit sia per gli indirizzi, sia per i dati. Si serve inoltre di un clock differenziale, un segnale latch di lettura/scrittura e un chip-select per ciascun dispositivo di memoria. L'interfaccia HyperBus supporta memorie RAM e flash esterne sul medesimo bus, e funziona con qualunque microcontroller dotato di un'interfaccia periferica compatibile con HyperBus.

L'interfaccia HyperBus è dotata di una configurazione master/slave in cui un host master si interfaccia con uno o più dispositivi di memoria slave sul bus. I dispositivi di memoria flash HyperBus sono designati con il nome HyperFlash, mentre quelli DRAM HyperBus con il nome HyperRAM.

Il bus utilizza un clock differenziale con segnali designati CK e CK#. Poiché l'interfaccia HyperBus è del tipo DDR, il trasferimento dei dati avviene sia durante il fronte di salita del clock, sia durante quello di discesa. Il clock è pilotato soltanto dal dispositivo master, e la sua frequenza non può essere superiore a quella nominale della memoria HyperBus più lenta presente sul bus.

Il bus bidirezionale a 8 bit è designato DQ[0-7], e trasferisce indirizzo, dati e comandi fra il dispositivo master e quelli slave. Come meccanismo di chiusura dei dati viene utilizzato un segnale di mancata eccitazione dei dati di lettura/scrittura, designato RWDS. Il segnale RWDS è controllato da qualunque dispositivo stia effettuando la lettura dei dati, quindi se l'host del microcontroller sta scrivendo i dati su un dispositivo HyperRAM, quest'ultimo controlla il segnale RWDS. I dati in via di lettura su DQ[0-7] sono allineati con entrambi i fronti del clock.

Ciascun dispositivo slave viene selezionato utilizzando un chip-select attivo basso, designato CS0#, CS1#, CS2# e così via. Può essere attivo un solo chip-select alla volta. Tutte le operazioni del bus iniziano con la transizione del chip-select designato da alto a basso. Tutte le operazioni del bus terminano con la transizione del chip-select designato da basso ad alto. Gli sviluppatori devono garantire che sia attivo un solo chip-select alla volta. In caso contrario, è possibile che più dispositivi slave HyperBus slave pilotino contemporaneamente il segnale RWDS, danneggiando i dati.

Il dispositivo master pilota un segnale di ripristino hardware attivo basso, designato RESET#. Quando viene portato al livello basso, tale segnale ripristina lo stato di tutti gli eventuali dispositivi di memoria HyperBus ad esso collegati. Tale operazione include il ripristino dei registri di configurazione interni dei dispositivi di memoria. Questa non influisce tuttavia sullo stato della memoria interna dei dispositivi di memoria HyperBus. Nella maggior parte delle interfacce con microcontroller master HyperBus, il segnale RESET# non fa parte della periferica HyperBus, ma è invece un pin di I/O generico. I dispositivi slave HyperBus sono dotati di un debole pull-up sul pin RESET# che, se lasciato flottante, viene portato in uno stato alto.

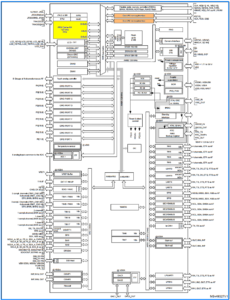

Qualunque periferica compatibile con HyperBus presente su un microcontroller deve essere conforme alla specifica HyperBus. Un buon esempio di microcontroller compatibile con HyperBus è il modello STM32L4R9 Arm Cortex-M4F di STMicroelectronics (Figura 1). Il modello STM32L4R9 è dotato di 2 Mbyte di memoria flash interna e di 640 kbyte di SRAM. È dotato di un'ampia gamma di periferiche, comprese due interfacce OctoSPI configurabili come interfacce HyperBus.

Il microcontroller STM32L4R9 accede agli indirizzi delle memorie esterne HyperBus come memoria mappata nello spazio degli indirizzi del bus AHB del microcontroller stesso, quindi il core accede in lettura e scrittura alla memoria esterna e a quella interna allo stesso modo. Una volta configurati i dispositivi di memoria esterna, il funzionamento dei dispositivi HyperBus è trasparente per il core.

Le memorie HyperBus sono tutte del tipo a 16 bit, quindi tutti gli accessi dal microcontroller STM32L4R9 devono avvenire sui limiti delle memorie a 16 bit. Gli accessi ai dati dal master STM32L4R9 possono essere a 16 bit o 32 bit, e devono avvenire anch'essi su limiti allineati.

Una tipica operazione di lettura o scrittura su HyperBus consiste in una serie sequenziale di trasferimenti di dati a 16 bit della durata di un ciclo di clock tramite due trasferimenti di dati a 8 bit corrispondenti della durata di mezzo ciclo di clock, uno su ciascun fronte di clock a terminazione singola o crossing di clock differenziale. Le operazioni di lettura e scrittura trasferiscono sempre parole di dati a 16 bit complete. Le parole dei dati di lettura contengono sempre due byte validi. Le parole dei dati di scrittura possono avere uno o entrambi i byte mascherati per prevenire la scrittura di singoli byte nell'ambito di un burst di scrittura. Il protocollo HyperBus non supporta i trasferimenti di byte né le operazioni sui bit, come quelle di bit-banding.

Ciascuna porta compatibile con HyperBus del microcontroller STM32L4R9 dispone di 256 Mbyte dedicati di spazio per indirizzi mappato in memoria come segue:

- Da HyperBus1 (OctoSPI1) 0x90000000 a 0x9FFFFFFF

- Da HyperBus2 (OctoSPI2) 0x70000000 a 0x7FFFFFFF

L'indirizzo interno del dispositivo di memoria HyperFlash o HyperRAM cui è in corso l'accesso presenta un offset rispetto all'indirizzo di memoria base della suddetta posizione. Se effettua la lettura dalla posizione di memoria 0x90000047, ad esempio, il microcontroller STM32F4L9 esegue il read-back del valore memorizzato nel dispositivo di memoria cui ha effettuato l'accesso su HyperBus1 nella posizione di memoria 0x0047.

Oltre ad avere sviluppato la specifica HyperBus, Cypress Semiconductor offre anche una linea di memorie HyperBus. La memoria HyperFlash S26KS512SDPBHI020 da 64 MB x 8 di Cypress è in grado di interfacciarsi facilmente con una delle porte OctoSPI. Supporta gli accessi burst con wrap fino a un massimo di 32 parole di 16 bit. Grazie a velocità di clock fino a 166,6 MHz, la memoria HyperFlash S26KS512 supporta una velocità di lettura sostenuta di ben 333 Mbps. Alla velocità massima del clock OctoSPI, pari a 60 MHz, il microcontroller STM32L4R9 è in grado di leggere qualunque memoria esterna HyperBus a una velocità massima di 120 Mbps.

Se l'accesso alla memoria HyperFlash avviene tramite il bus di sistema Cortex-M4, il microcontroller STM32L4R9 è in grado di eseguire il codice direttamente da tale memoria flash. Quando viene utilizzata per la memoria del codice, la porta OctoSPI supporta la funzione eXecute In Place (XIP) con un buffer di pre-fetch integrato che carica l'indirizzo di memoria successivo dalla memoria esterna.

La memoria HyperRAM S27KS0641DPBHI020 da 8 MB x 8 di Cypress Semiconductor è una DRAM ad auto-aggiornamento in grado di fungere da espansione della memoria dati del microcontroller STM32L4R9. Supporta gli accessi burst con wrap fino a un massimo di 64 parole di 16 bit. La memoria HyperRAM S27KS0641 supporta inoltre velocità di lettura sostenute fino a 333 Mbps, e può essere letta dal microcontroller STM32L4R9 a una velocità massima di 120 Mbps.

Interfacciamento con le memorie HyperBus

Il microcontroller STM32L4R9 è dotato di due porte compatibili con lo standard HyperBus, ciascuna delle quali è in grado di interfacciarsi separatamente con dispositivi di memoria esterni HyperRAM e HyperFlash (Figura 2). Il segnale RESET# è opzionale, e non è pertanto mostrato nella figura. Le memorie HyperFlash e HyperRAM di Cypress consentono di espandere facilmente la memoria interna del microcontroller STM32L4R9 con un impatto minimo sulle dimensioni delle schede CS e sulla complessità di progettazione.

I segnali più importanti per il layout sono DQ[0-7] e RWDS. Per ottenere le massime prestazioni, tali segnali devono seguire il più breve percorso possibile sulla scheda CS tra il microcontroller e la memoria.

I segnali CK e CK# del clock differenziale devono trovarsi l'uno accanto all'altro, a una distanza costante per l'intera lunghezza del percorso. Se possibile, schermare CK e CK# con piste di guardia VSS per ridurre al minimo le interferenze EMI. Per ridurre al minimo il disadattamento di impedenza, separare tutti i segnali sullo strato superiore delle schede CS, con uno strato solido VSS al di sotto.

Per gli sviluppatori senza una buona conoscenza dello standard HyperBus, è una buona idea aggiungere punti di tastatura. Nel caso dei segnali DQ[0-7] e RWDS, devono di preferenza essere presenti punti di prova sia sul microcontroller STM32L4R9, sia sul dispositivo di memoria. Quando il microcontroller STM32L4R9 sta eseguendo operazioni di scrittura, è buona prassi osservare i punti di prova più vicini al dispositivo di memoria. Quando il microcontroller STM32L4R9 sta eseguendo operazioni di lettura, osservare i punti di prova più vicini ad esso. Disporre i punti di prova dei segnali CK, CK# e CS più vicini al dispositivo di memoria.

A causa delle elevate frequenze di clock dell'interfaccia DDR, è importante che l'alimentazione di tensione del microcontroller STM32L4R9 e dei dispositivi di memoria sia il più pulita possibile. Un'alimentazione rumorosa influisce negativamente sulla temporizzazione dei segnali e può causare errori di trasferimento sul bus, quindi si consiglia l'adozione di condensatori di disaccoppiamento. I dispositivi di memoria HyperBus sono dotati di alimentazione e terra separate per i pin di I/O, ed è opportuno aggiungere al VCCQ dell'alimentazione di I/O condensatori da 1 e 0,1 µF sullo strato superiore e inferiore.

Accesso del firmware ai dispositivi HyperBus

I dispositivi di memoria HyperBus sono dotati di registri su chip utilizzati per impostare opzioni e temporizzazioni del dispositivo stesso. Lo standard HyperBus indica tali elementi come registri di configurazione (CR). Tutti i dispositivi HyperRAM dispongono di CR che consentono di impostare determinate caratteristiche di funzionamento. Nel caso del modello HyperRAM S27KS0641, il firmware è in grado di configurare le modalità a basso consumo, il tipo e la durata di burst con wrap, i parametri di temporizzazione R/W e l'energia con cui viene pilotata l'uscita sul bus dati esterno a 8 bit.

Le memorie HyperFlash non dispongono di CR, ma sono dotate di registri di stato. Il modello HyperFlash S26KS512 possiede tre registri di stato. Supporta un codice di correzione errori (ECC) interno per la convalida delle operazioni di scrittura, e dispone di un registro di stato ECC per l'indicazione degli errori di scrittura. Un altro registro contiene l'indirizzo di tutti gli eventuali errori ECC. Un terzo registro effettua il conteggio delle correzioni ECC e degli errori che non è possibile correggere. Tutti i registri in questione sono di sola lettura.

Le operazioni HyperBus supportano due tipi di operazioni di memoria. Il primo è costituito dalla lettura o dalla scrittura su memorie esterne. Il secondo consiste nella lettura o nella scrittura su CR o registri di stato di lettura.

Una volta configurata una porta OctoSPI del microcontroller STM32L4L9 come porta HyperBus, il core è in grado di accedere alla memoria come a qualunque altra posizione mappata in memoria. Ogni operazione di lettura o scrittura nello spazio HyperBus mappato in memoria avvia un'operazione fra il microcontroller e la memoria esterna. Ogni transazione HyperBus inizia nel momento in cui il microcontroller invia al dispositivo di memoria esterno tre parole di 16 bit con istruzioni di comando/indirizzo. La sequenza di comando/indirizzo indica al dispositivo di memoria esterno se l'operazione è di lettura o di scrittura, se è indirizzata allo spazio di memoria o ai registri di configurazione e se l'operazione è di tipo burst con wrap o lineare, specificando inoltre la riga e la colonna dell'indirizzo di destinazione. Tutto questo è trasparente per il microcontroller con firmware operativo, ma la sequenza di comando/indirizzo è importante durante il debugging.

Primi passi con HyperBus

Una volta compreso il protocollo HyperBus, si consiglia di creare qualche programma sperimentale da eseguire con una scheda di valutazione; questo consiglio è rivolto soprattutto agli sviluppatori privi di esperienza con l'interfaccia. La scheda di valutazione STM32L4R9I-EVAL di STMicroelectronics per il microcontroller STM32L4R9 è un buon punto di partenza (Figura 3). Il cerchio rosso indica il dispositivo di memoria HyperRAM; i suoi punti di prova si trovano sul connettore basetta a destra.

La scheda STM32L4R9I-EVAL offre numerose caratteristiche, fra cui un'interfaccia foto/videocamera, due microfoni MEMS, un joystick e un display LCD TFT a colori da 4,3" e 480x272 pixel. La scheda di valutazione supporta l'interfaccia OctoSPI, e dispone di un dispositivo ISSI HyperRAM IS66WVH8M8BLL da 64 Mbit saldato sulla scheda CS.