Le flash NAND 3D stanno compiendo un grande passo in avanti. La nuova tecnologia di memoria ha ottenuto enormi progressi negli ultimi anni e offre un'interessante alternativa alle tecnologie affermate di memoria NAND 2D utilizzate nelle unità SSD. Le architetture di memoria di prossima generazione, come le NAND QLC, indicano la direzione dello sviluppo.

La tecnologia flash NAND 2D è impressionante con i suoi tempi di accesso estremamente rapidi, le latenze ridotte, i consumi contenuti, la robustezza e i fattori di forma ridotti. I principali progressi tecnologici puntavano alla riduzione dei costi attraverso la miniaturizzazione strutturale. Tuttavia, oggi si è raggiunto un limite fisico a 15 nanometri. Strutture sempre più piccole porterebbero a più errori durante la lettura dei dati e a una riduzione della robustezza e della ritenzione dei dati – in ultima analisi l’integrità dei dati nel lungo termine non sarebbe garantita. Pertanto, le innovazioni stanno andando nella direzione delle Flash NAND tridimensionali (3D NAND) e verso l’aumento del numero di bit per cella.

Le soluzioni attuali: dispositivi a intrappolamento di carica e a floating gate

In una memoria flash NAND 3D vengono impilati più strati di celle flash – in modo analogo ai piani di un grattacielo, migliorando così la capacità in modo significativo. Il paragone è semplificativo, ma la tecnologia sottostante è molto più complessa. Ad oggi, due approcci sono diventati standard: il floating gate e l’intrappolamento di carica. Sebbene differiscano totalmente nel modo in cui sono realizzati, l'idea alla base è simile. Con il metodo floating gate, le cariche sono memorizzate attraverso un gate flottante isolato elettricamente e situato tra il canale e il gate di controllo. Nelle architetture a intrappolamento di carica, per contro, le cariche sono trattenute all’interno di centri di intrappolamento, costituiti da uno strato di nitruro di silicio che è separato dal canale da uno strato sottile di ossido tunnel. In entrambi i casi, i livelli CG definiti sono selezionati tramite le linee del gate di controllo o wordline (WL). La stringa è selezionata attraverso le bitline (BL).

In una memoria flash NAND 3D vengono impilati più strati di celle flash – in modo analogo ai piani di un grattacielo, migliorando così la capacità in modo significativo. Il paragone è semplificativo, ma la tecnologia sottostante è molto più complessa. Ad oggi, due approcci sono diventati standard: il floating gate e l’intrappolamento di carica. Sebbene differiscano totalmente nel modo in cui sono realizzati, l'idea alla base è simile. Con il metodo floating gate, le cariche sono memorizzate attraverso un gate flottante isolato elettricamente e situato tra il canale e il gate di controllo. Nelle architetture a intrappolamento di carica, per contro, le cariche sono trattenute all’interno di centri di intrappolamento, costituiti da uno strato di nitruro di silicio che è separato dal canale da uno strato sottile di ossido tunnel. In entrambi i casi, i livelli CG definiti sono selezionati tramite le linee del gate di controllo o wordline (WL). La stringa è selezionata attraverso le bitline (BL).

La tecnologia di memoria NAND 3D offre numerosi vantaggi per i fornitori e anche per i clienti. La maggiore densità di memoria assicura che i fornitori di memorie flash possano produrre dispositivi con capacità superiori e con più gigabyte in un wafer di silicio, a parità di resa. I clienti beneficiano di una notevole riduzione di prezzo, pur ottenendo la stessa durata operativa.

Tuttavia, non è ancora stato introdotto un prodotto 3D NAND con una resistenza elevata alla temperatura, come spesso è richiesto dal mercato. I primi prodotti NAND 3D che sono adatti per temperature industriali dovrebbero essere lanciati nel 2019.

Flash NAND QLC

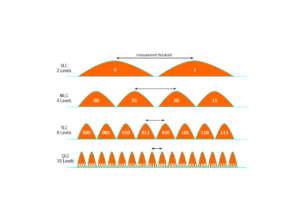

È possibile ottenere una maggiore densità di memoria non solo impilando le celle di memoria, ma anche aumentando la capacità delle celle presenti. Quando la tecnologia NAND venne introdotta per la prima volta, era disponibile unicamente l'architettura a singolo livello (SLC). In altri termini, era possibile memorizzare un bit in ogni cella di memoria. Successivamente si sono aggiunte le tecnologie con cella multilivello (MLC) e con cella a triplo livello (TLC), che sono in grado di memorizzare due o tre bit per cella, rispettivamente. Ora, le flash NAND QLC, la generazione successiva alle architetture NAND 3D, sono appena dietro l'angolo. QLC sta per "cella a quadruplo livello" o "quad level cell" e quindi memorizza quattro bit per cella. Questa architettura supporta attualmente fino a 96 livelli. La quarta generazione di Micron e la quinta generazione di Samsung, SK Hynix e Toshiba dovrebbero consentire di impilare fino a 128 livelli. (Figura 1)

Più capacità, meno durata

Il vantaggio principale delle memorie flash QLC è la densità considerevolmente più alta di memoria e quindi la maggiore capacità. Di conseguenza, è possibile ottenere formati più piccoli, e i rack dati possono avare dimensioni fino a 7,7 volte inferiori rispetto a quelli che utilizzano dischi rigidi, risparmiando così spazio prezioso all'interno dei data centre.

Ciò nondimeno, l'architettura QLC presenta anche alcuni punti deboli. Sono presenti 16 diverse tensioni per ogni cella di memoria, il che rende la scrittura dei dati un compito più complesso e più lento. (Figura 2) Inoltre, l'affidabilità della memoria diminuisce. La validazione dei singoli bit è più stringente e le celle degradano dopo diversi cicli di scrittura, rendendo difficile la determinazione dei valori dei singoli bit. Questo può dare origine ad errori sui dati. L’ECC (codice di correzione di errore) è utile in questo caso, ma non è sufficiente per compensare tale effetto. Ciò inoltre influisce negativamente sulla durata delle memorie QLC: con 500 fino a 1.500 cicli di P/E (programmazione/cancellazione, cicli di scrittura e di cancellazione), la durata è significativamente inferiore rispetto a quella di un'architettura 3D TLC e notevolmente inferiore rispetto ad un'architettura SLC.

Siamo pronti per le applicazioni dei Big Data

Tuttavia, l'uso delle memorie flash QLC è indicato in molti campi di applicazione. A causa del loro numero ridotto di cicli di P/E, le memorie sono pensate principalmente per le operazioni di lettura (per il 90% o più). Le memorie QLC possono essere utilizzate ovunque sia necessario leggere rapidamente grandi quantità di dati, ma siano necessari solo pochi processi di scrittura. Ciò include, ad esempio, l’analisi in tempo reale di grandi quantità di dati, l'analisi dei dati in ingresso per le intelligenze artificiali, la fornitura di contenuti multimediali per i servizi on-demand, i database NoSQL e l'autenticazione degli utenti. Per questi tipi di applicazione, il TCO (costo totale di gestione) è inoltre significativamente inferiore rispetto a quello dei dischi rigidi, poiché il numero totale di unità di memoria necessarie è molto più basso, viene consumata meno energia e sono elaborati più IOPS. Grazie all’alta densità di memoria, è anche possibile pensare ad applicazioni nel mercato embedded.

5210 ION: il primo SSD QLC

In collaborazione con Intel, Micron ha lanciato il primo prodotto QLC: la serie di SSD Enterprise 5210 ION, che si basa su interfaccia SATA. L’SSD si avvale di un’architettura a quattro bit per cella con un totale di 64 strati di celle. È possibile memorizzare da 1,92 a 7,68 terabyte in un formato di appena 2,5 pollici. Le velocità dati sequenziali sono pari a circa 500 Mbps in lettura e 340 Mbps in scrittura. La serie 5210 ION è essenzialmente progettata per soddisfare i requisiti delle applicazioni che comportano un grande numero di operazioni di lettura su cloud.

In collaborazione con Intel, Micron ha lanciato il primo prodotto QLC: la serie di SSD Enterprise 5210 ION, che si basa su interfaccia SATA. L’SSD si avvale di un’architettura a quattro bit per cella con un totale di 64 strati di celle. È possibile memorizzare da 1,92 a 7,68 terabyte in un formato di appena 2,5 pollici. Le velocità dati sequenziali sono pari a circa 500 Mbps in lettura e 340 Mbps in scrittura. La serie 5210 ION è essenzialmente progettata per soddisfare i requisiti delle applicazioni che comportano un grande numero di operazioni di lettura su cloud.

Con la terza generazione di memorie NAND 3D ancora in fase di sviluppo, Micron intende offrire la più alta densità di gigabit per millimetro con un totale di 96 strati. Altri fornitori saranno presto in grado di lanciare le loro prime soluzioni QLC: Intel, che sta attualmente sviluppando la propria tecnologia di memoria NAND 3D indipendentemente da Micron, ha annunciato di recente la produzione del primo SSD basato su memoria QLC con interfaccia PCIe e Toshiba Memory prevede di avviare la produzione in volumi della NAND QLC BiCS4 nel 2019. Come partner di Apcacer, Intel, Swissbit, Toshiba, Transcend e Wilk, Rutronik è a stretto contatto con i principali fornitori di memorie dati. Il team di Rutronik Storage fornisce gli sviluppatori e agli acquirenti un supporto e una consulenza completa nella selezione della tecnologia di memoria più adatta.